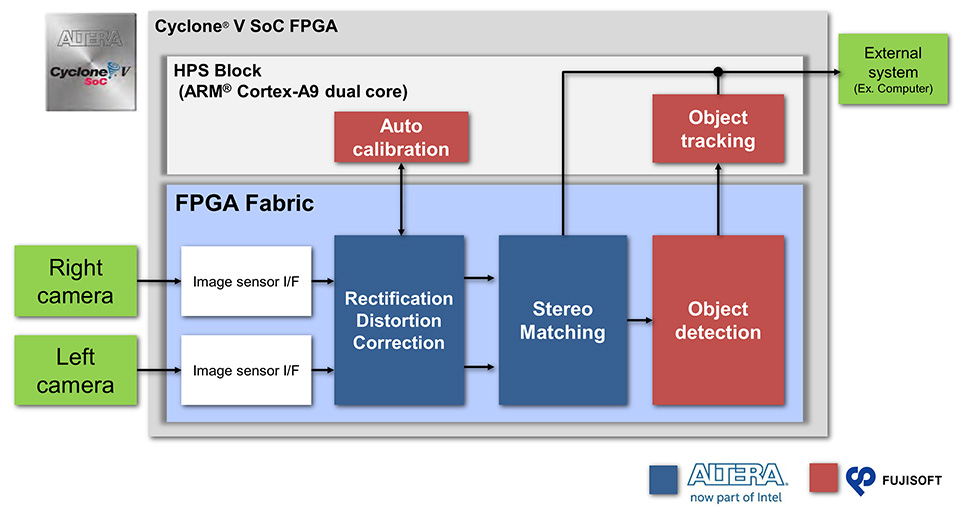

Distance measurement sensor hardware & software development implemented into Stereo camera

| Responsibility | [Hardware] Object detection IP, Object tracking IP, FPGA design, Tests [software] Driver(s), Control application(s) |

|---|---|

| Key technologies | Electronic circuit RTL language, C language |

| Circuit design | FPGA |

| FPGA design | several controllers |

| Driver development | PC deriver(s) |

| Application development | Distance measurement sensor control application(s) |