COLUMN

物体検出と物体認識をDeep Learningと小型SoC FPGAと既存センサーでデモ構築せよ!

今回のコラムは、YoloやSSDに代表される画面上の物体を見つける物体検出と見つけた物体が何かを分類する物体認識を数千円レベルの小型FPGAを使って既存のセンサーとの組み合わせで実現できるのか?というチャレンジ回想録です。無理難題を突き付ける上司の課題を、淡々とある時はバッサリと片づけるエンジニアが取り組むデモシステム開発の裏側を、コラム形式で公開します。

突然のオーダー。予算も時間も無いんだけど・・

「今度の展示会の件だけど。」 突然肩越しに室長の声がした。FPGAを主体にした、何かインパクトの有るカッコイイAIデモをやれないか?とういう相談である。いや、相談というのは適切ではない。いつものようにオーダーである。10分間の立ち話の結果、「映像で四角い枠で車とか人とかを囲むやつがあるよね。あんな感じがうけるし、AIってパット見わかるでしょ~。いや、デモレベルでいいんだから。じゃ来週月曜日に。検討よろしくね~。」 いつものように一方的に話は終わった。

月曜の午後、「例のデモ、いつまでにできる?予算は無いけど。」肩越しに室長の明るい声がした。 もちろん、やるとは言っていないし、ましてや、出来ると一言も言っていないのだが、室長の中では既に決定事項のようである。 ・・えっ?ちょっと待った!予算が無い? 耳を疑い振り返ると、室長はいなかった。

さて、先ずはAIの検討から。デモの主なAI機能は2つ、画面上にある物体を見つける機能(物体検出)と、その物体がどの分類にわけられるのかを推論する機能(物体認識)の連携である。先ずは基本的な物体認識の機能実現について取り組むことにした。手持ちの機材は、インテル ® Arria ® 10 GXの評価ボード1枚とインテル® Cyclone ® VのDE10nano評価ボードが2枚。学習環境用のオンプレ・サーバーとNVIDIA社のグラボ1枚である。

関連ソリューション

物体認識なら何とかできる?

1. CNN(畳込みニューラルネットワーク)をFPGA化する技術

2017年3月にドイツの展示会でインテル® Arria®10 SoC FPGAを使って、畳み込みニューラルネットワーク(CNN:Convolutional Neural Network)の推論を参考技術展示したことがあった。当時はインテル® Xeon® 搭載のサーバーにウン十万円のArria® 10GX評価ボードをくみあわせて、Alexnetの浅いCNNを正直に実装した、まさに、力ずくでニューラルネットワークを回路化した巨大な技術デモだった。 当時は画期的であったが、今となっては・・・ 新しさに欠ける・・・

今回は展示スペースも限られるので、ドでかいサーバーは置けない。以前のデモから進化したものでなければ意味が無い。リアルタイム映像を使った実践的AI処理で具体的な用途をイメージできるデモにしたい。・・と思いは広がる。

<2値化CNN技術の説明>

実は、物体認識については方策があった。某大学研究室と連携して、既に社内で基礎研究と評価を進めていた2値化畳込みニューラルネットワーク技術が使えるのではないかと。

聞きなれない2値化畳込みニューラルネットワークについては、少し説明が必要かもしれない。

先ずはAIの常識の確認だ。 一般的にディープラーニング(深層学習)ではNVIDIA社に代表されるGPUを使ってAIの開発、主に学習が行われている。学習用には大きなバッチサイズの行列演算をFP32(32ビット精度の浮動小数点)や、FP16(16ビット精度の浮動小数点)の演算精度で、ニューラルネットワークの構成を行うのだが、モデル毎の特徴量や重みを探し出すために様々なパラメータで試行錯誤を繰り返す推論の演算を何千万回と繰り返すことで、そのモデルを分類するための特徴や重みを探し出す作業である。

簡単に言うと、AIの学習作業は大量の計算とデータを使って色々な組み合わせを検討して検証しての繰り返し作業を膨大な回数繰り返す作業なのです。(人間に当てはめる、試験勉強では理解したり覚えるために時間をかけて演習問題を解いたり、参考書を読み返したりしながら、自分の頭の中で理解を組みたてていく感じと、何となく似ている。)

それと同じ開発環境で推論を動かすのが通例であったために、推論時もFP32やFP16の演算精度で計算していたが、実は推論用の演算では高い演算精度が不要なのである。

実際、最近では推論の計算では8ビット整数演算精度で十分だというのが常識です。

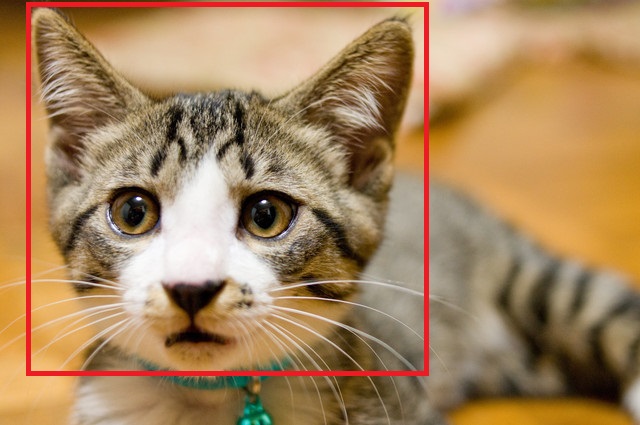

この考え方を突き詰めていくと、究極の選択は、YesかNoの2択となる。つまりネコ判定のニューラルネットワークで判断されるのは、「これがネコなのか?」それとも、「ネコではないのか?」の2択。このようにAIの推論、特に分類するような処理ではFP32のような高い演算精度が必要ではないのが何となくお分かりになるのではないでしょうか?

ネコ推論のニューラルネットワークの中の学習計算では特徴を見つける計算作業として、元の画像からその形や特徴的なモノを捉え、そこからネコに共通する部分を見つけるのですが、推論ではそのぼんやりとした特徴的なところと目の前の物体とで一致するとこがあるかどうかを判定するだけなのです。そして判定した結果、一致するところが多いと、「これはネコっぽい特徴が多いから、多分ネコだと思われる!」ということになる。

前置きが長くなりましたが、2値化畳込みニューラルネットワークとは畳込みニューラルネットワークの入力値と重みを2値(+1と⁻-1)にし、積和演算を単純処理に置き換え、内部で扱うデータも単純にすることで、超シンプルなニューラルネットワークを構成できる手法なんです。シンプルということはそれを実現するためのロジック(回路)もシンプルにできるということで、小型のAIを作れる可能性がある技術の一つです。但し、この技術は推論専用なんです。つまり、推論専用のAIを小さく作る技術として2値化という手法が使われてるんですね。小さく作るという意味は、電子回路に例えると、少ない回路でAIをくみ上げるということになります。これをFPGAという半導体チップに置き換えると、より回路規模の小さなFPGAチップにAI推論機能を入れる。つまり、ワンチップのAIが作れる技術というわけです。

インテル® Cyclone®-V SoCでも2値化すれば畳込みニューラルネットワークが動く?

2値化畳込みニューラルネットワーク技術を使うことで、ニューラル内で使われる入力値と重みを単純化することで、複雑な演算回路、特に掛け算の回路を論理回路に置き換えられて、驚くほど簡単な回路になる。ということは、ニューラルネットワークを実現するために必要なハードウェアリソースを少なくすることができる。つまり、小型のFPGAでも推論AIを組み込んでしまえる可能性があるというわけだ。

早速、手持ちのIntel社の小型SoC FPGA:インテル® Cyclone®-Vが搭載された『DE10nano』評価ボードの出番かもしれない!

と、エンジニア魂に火がついてしまった私であった。

この時点で、展示会当日まで残された時間は61日と23時間であった。

つづく・・・

個別相談も承っております。下記よりお申し込みください。