COLUMN

【Intel® アクセラレーションカード開発日誌 #4】 Intel® アクセラレーションカードの開発方法

前回はIntel® Programmable Acceleration Card(以降Intel® アクセラレーションカードと呼称)のDMA速度の測定と、測定結果からの性能の考察を行いました。今回からは、いよいよIntel® アクセラレーションカードの開発を始めていきます。

ベースはサンプルデザインで

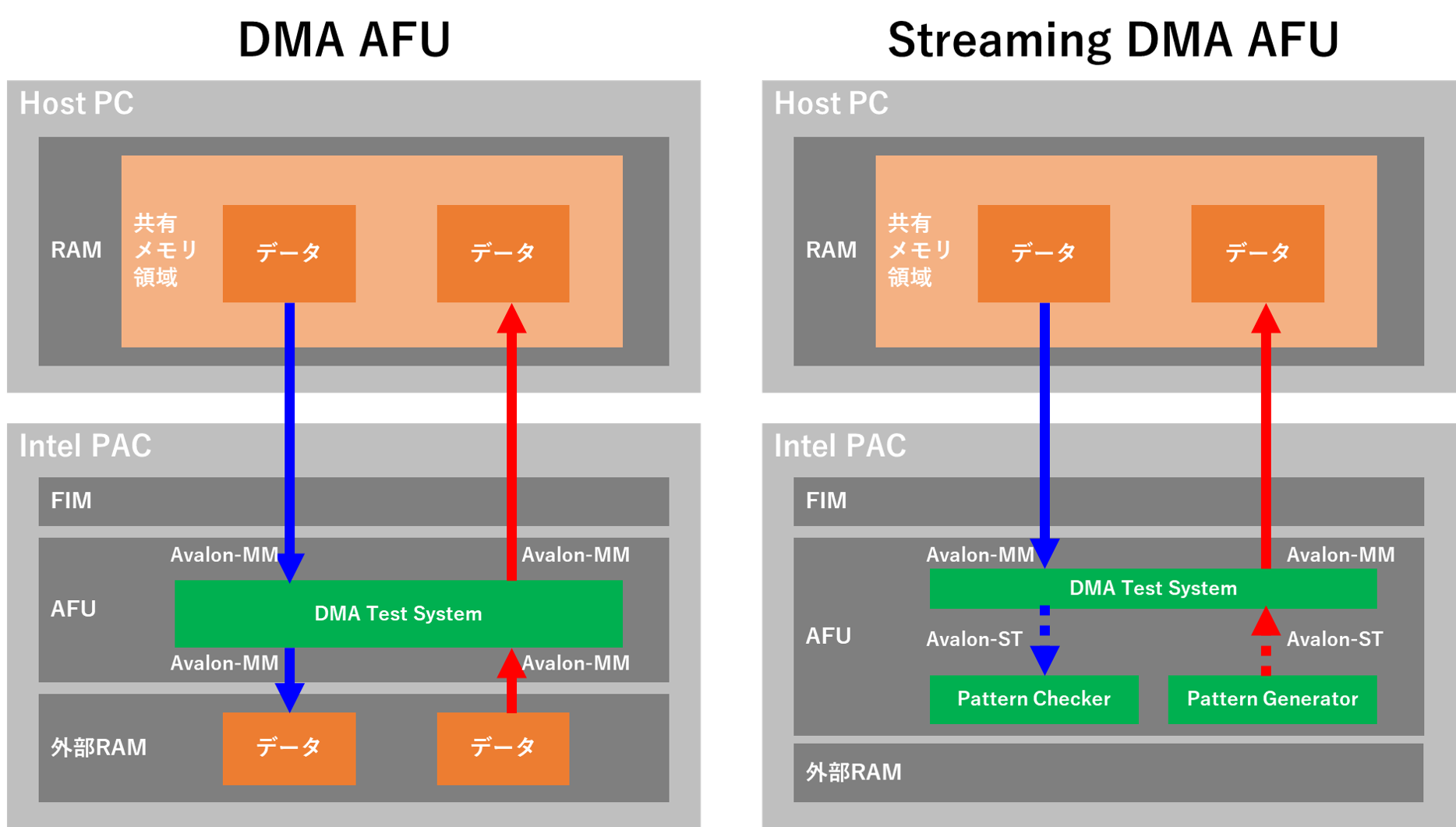

前回は基本的な2つのサンプルDMAデザインが用意されているという話をしました(図1)。

データの塊を共有メモリからIntel® アクセラレーションカードのローカルメモリにコピーしてくるDMA AFU (https://www.intel.com/content/www/us/en/programmable/documentation/tmv1511227122034.html)と、データを順次Intel® アクセラレーションカードにストリームデータとして転送するStreaming DMA AFU (https://www.intel.com/content/www/us/en/programmable/documentation/ctb1526061110715.html)です。いずれも、デザインを解説するドキュメントも用意されています。

本稿では、Intel® アクセラレーションカードに映像データ処理IPコアを実装する開発を行います。このIPコアはSDIストリーム信号を入出力とする仕様になっているので、今回はStreaming DMA AFUをベースに開発していきます。

Intel®社公式のAFU設計ガイドであるAccelerator Functional Unit (AFU) Developer’s Guide (https://www.intel.com/content/www/us/en/programmable/documentation/bfr1522087299048.html) と並行しながらご覧ください。

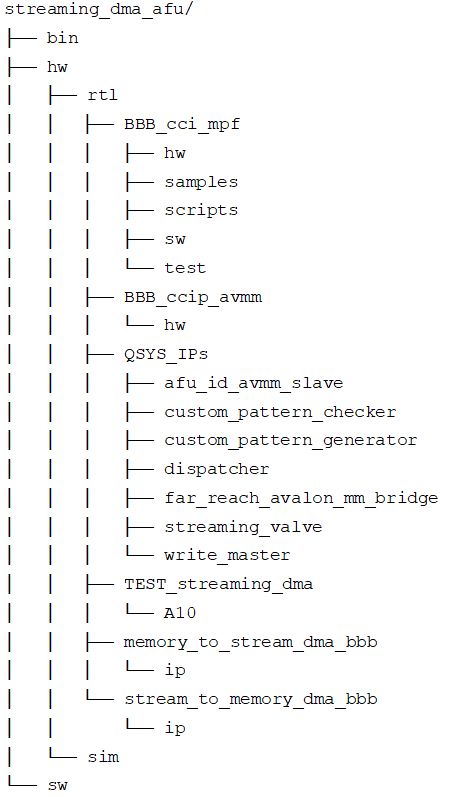

AFUデザインのフォルダ構成

Streaming DMA AFUのサンプルデザインは、以下の場所にあります。

$OPAE_PLATFORM_ROOT/hw/samples/

(なお、$OPAE_PLATFORM_ROOTは、Intel®Acceleration Stackをインストールした際に指定される、OPAEのRootディレクトリです。詳細はIntel® アクセラレーションカード開発日誌#2を参照してください。)

さて、サンプルデザインをQuartus Primeで開いて中身を見てみようとするのは、設計者が行う第一歩目ですが、これらのディレクトリの中をいくら探してもqpfファイル(Quartusのプロジェクトファイル)がありません。

実は、qarファイルを含むワークディレクトリと一部のQuartus用ファイルは、afu_synth_setupというコマンドで生成される仕組みになっています。

サンプルデザインのディレクトリの最上位階層で、以下のコマンドを実行します。

$ afu_synth_setup --source hw/rtl/filelist.txt build_synth

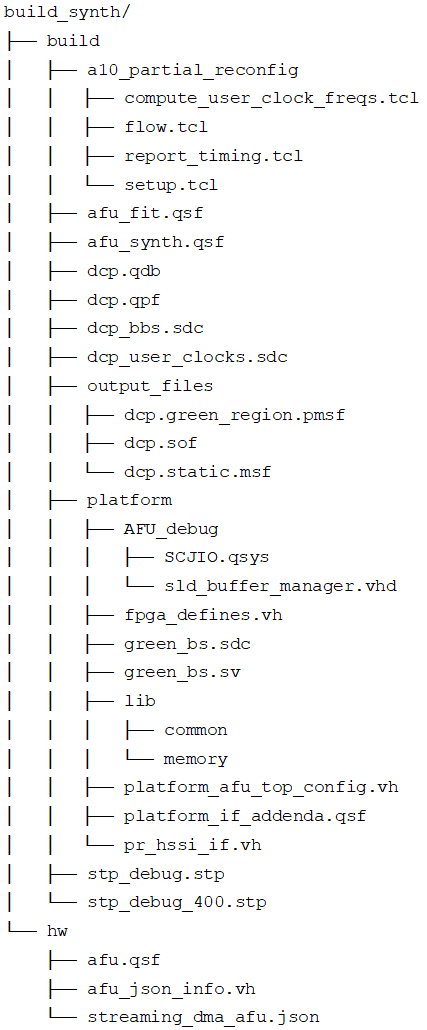

build_synth/build の下に、やっとqpfファイルが出てきました!sdcファイルやqsfファイルも!おなじみのファイルが出てきて嬉しくなりますね。

つまり、build_synth/build が、Quartus Primeのワークディレクトリということになります。

afu_synth_setupコマンドの引数では、filelist.txtを指定していて、このファイルの記載を元にQuartus Primeのワークディレクトリのファイルを生成しています。

このfilelist.txtはビルドコンフィギュレーションファイルと呼ばれる、AFUのデザインソース(RTL、IP、Platform Designerサブシステム、制約など)、必要なマクロ定義とインクルードファイル、jsonファイルも含めた全てのファイルのパスをリストしたものです。

このfilelist.txtこそが、プロジェクトに必要なあらゆるファイル情報が記載されており、AFUデザイン管理の要ということになります。

さて、build_synth/build に移動し、qpfファイルをQuartus Primeで開いてみましょう。

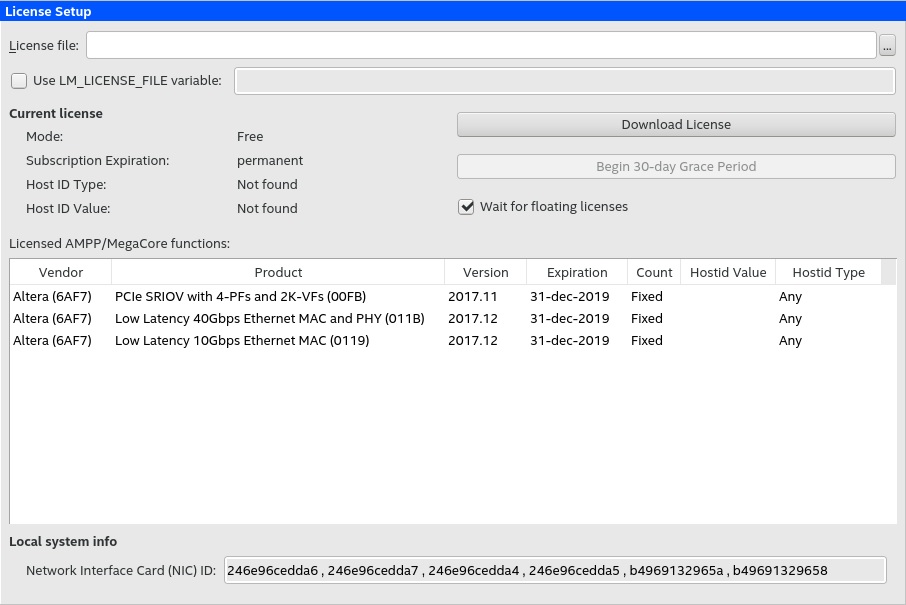

念のためにQuartusのライセンスを確認すると、Intel® アクセラレーションカードの開発に限ったローカルライセンスとなっていることがわかります(図3)。Intel® アクセラレーションカード開発専用Quartus Primeということですね。

AFU開発のツールフロー

Quartus Primeでdcp.qpfを開くとわかりますが、dcp.qpfには2つのリビジョンが含まれています(図3)。

Error(xxxx): Top-level design entity “dcp_top” is undefined

というエラーが出て失敗します。

afu_synthはビルド用のリビジョンです。サンプルデザインからデザイン修正して開発する際は、このリビジョンをベースに開発用のリビジョンを作成することが推奨されています。Top-lebel design entityはgreen_bsで、このままコンパイルするとfitterで

Error(xxxx): Running the Fitter on a partial reconfiguration design at the synthesis revision is illegal.

というエラーで失敗します。余談ながら、green_bsはGreen Bit Streamのことで、Intel® アクセラレーションカードの開発版ではAFUをGreen Bit Stream、FIMをBlue Bit Streamと呼ばれていた頃の名残です。

結局、どっちもビルドに失敗するんかよ!と思われたかと思いますが、Intel® アクセラレーションカードのデザインのビルドは、Quartus PrimeのUIではなく、コンソールのコマンドラインで行うことになっています。

先程のafu_synth_setupコマンドで生成された、build_synthディレクトリの下で、以下のコマンドを実行することで、ビルドが開始します。このとき、run.shの中で参照されるリビジョンは、afu_synthのみです。

$ $OPAE_PLATFORM_ROOT/bin/run.sh

ビルドが完了すると、同じディレクトにgbsファイルが生成されます。これがIntel® アクセラレーションカードのAFUにロードされるFPGA回路データです。

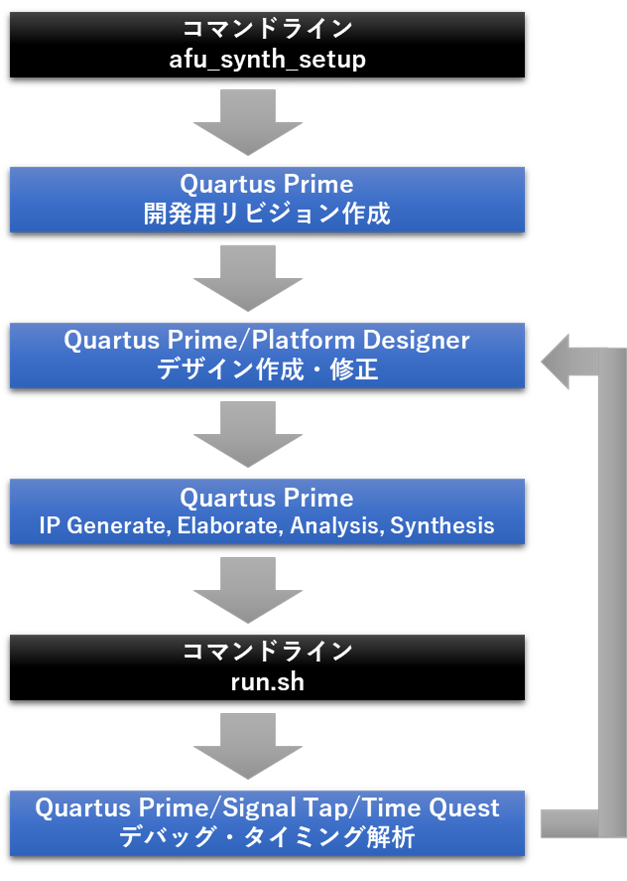

こういったツールフローが非常にわかりにくく、これまでIntel® FPGA開発を行ってきた人でも気をつける必要があります(図4)。

さて、Accelerator Functional Unit (AFU) Developer’s Guideの推奨どおりに、afu_synthをベースにした、開発用のリビジョンafu_devを作成します。

そして今後は、afu_synthは触らずに、afu_devのデザインを変更していきます。

Quartus Primeの操作先のリビジョンをafu_devにしている状態で、Platform Designerを起動します。このとき、qsysファイルの場所を聞かれますが、はて、最上位階層のqsysファイルはどこにあるのでしょう。

これもなかなか分かりづらいのですが、Streaming DMA AFUの場合は以下の場所にあります。

streaming_dma_afu/hw/rtl/TEST_streaming_dma/A10/streaming_dma_test_system.qsys

これでやっと、デザインの概要が把握できるところまできました。

ここまでくると、このPlatform Designerで回路変更し、HDL generateし、Quartus PrimeでSynthesis まで実行し、コマンドラインでrun.shを実行してビルドする、という手順が見えてきましたね。

試しに、全くデザイン変更することなく、HDL generateからrun.sh実行までを行ってみてください。無事にgbsファイルが生成されたら、それをfpgaconfコマンドでIntel® アクセラレーションカードにデプロイしてみましょう。

swディレクトに入っているサンプルソフトウェアをビルドし、実行することでエラーが出なかったら、Intel® アクセラレーションカードの開発手順に間違いはなかったことになります。

以上、Intel® アクセラレーションカードの開発手順に置いて、従来のIntel® FPGAとは異なる部分を中心に説明してきました。Intel® FPGAの開発手順そのものについては、Intel社や、Intel社のFPGA代理店、マクニカ社が様々な資料を提供しており、トレーニングも行っているので、各社にお問い合わせください。

個別相談も承っております。下記よりお申し込みください。