COLUMN

[FPGA開発工程のちょっとしたこだわり]インプリメントの基本

KUMICOをご覧の皆さまこんにちは!

さて、今回も“初めてFPGA開発をします!”という新人さんに向けて、

前回の掲載「論理シミュレーション工程のおさえておくべき基本」に引き続き、

インプリメント(論理合成/Fitting)工程についてお話しようと思います。

関連ソリューション

FPGA設計・開発ソリューション

今回は“ちょっとしたこだわり“というよりは、便利なインプリメントオプションを紹介します!

★インプリメントとは

VHDLやVerilog-HDL等を使用してコーディングした論理回路を、Intel(Altera) FPGAやXilinx FPGAに書き込む為のコンフィグレーションデータを作成することです。

使用するツールは、Intel(Altera)FPGAの場合はQuartus® Primeツール。Xilinx FPGAの場合はVivadoツールを使用します。

ツールを使用して主に以下の作業を行います。

・ターゲットデバイスの設定

・RTLファイル読み込み

・PINアサイン設定

・タイミング制約

・コンパイル(論理合成/Fitting)

・ワーニングチェック

・タイミングチェック

・コンフィグレーションデータ作成(←FPGAに書き込むデータが完成)

ツールの使用方法は、ベンダーが提供している資料に詳しく説明されておりますのでそちらをご参照下さい。

今回はIntel(Altera)社のQuartus Primeで私がよく使った便利なオプションをご紹介します。

■回路規模の確認

インプリメントの工程では、回路規模という概念が重要になります。

Intel(Altera)FPGAにはロジック・エレメント(LE)というデバイスの規模(容量)を示す単位があり、コンパイル時にRTL(論理回路)をロジック・エレメント(LE)に割り当てられます。

RTL(論理回路)の規模がロジック・エレメント(LE)数を超えてしまう場合は、コンフィグレーションデータを作成することができません。

そもそも、インプリメントはTOPソースを含め、全てのRTLを纏めてコンパイルするものですが、まずは自分が設計した一部の下位モジュールだけの回路規模を確認したい時があります。

それではどのように回路規模を確認するかご説明します。

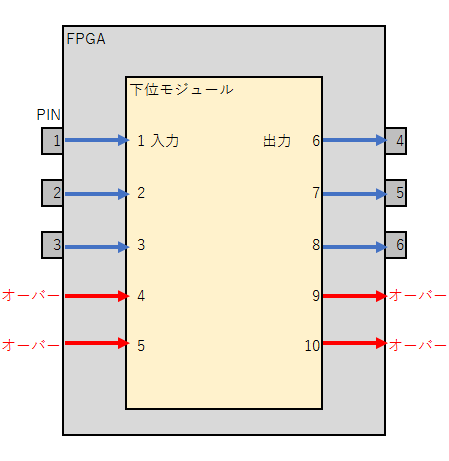

本来あるべきTOPモジュールはFPGAのPIN数を意識して入出力信号数を決めますが、下位モジュールはPIN数を意識する必要はないため、このようなエラーになることがあります。

こんなイメージです。(例えば6PINしかないFPGAに、10本の入出力信号がある下位モジュールをコンパイルした場合)

エラーになって回路規模を確認できない・・・そんなとき以下の方法で行います。

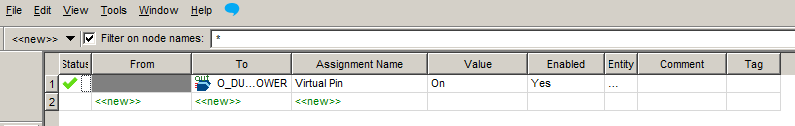

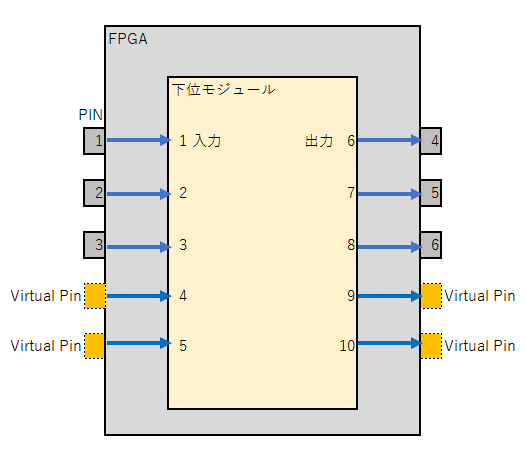

「Assignment Editor」を開き、下位モジュールの入出力信号に“Virtual Pin” オプションを設定します。

“Virtual Pin“で設定された入出力信号は、その名の通りVirtualなFPGAのPINとして割り当てられる為、エラーを回避することができます。こんなイメージです。

コンパイル後に、「xxxxx.fit.rpt」レポートが出力されますので、Fitter Summaryで回路規模をご確認下さい。

(この回路規模は目安としてお考えください)

※FPGAについて

FPGAとは、Field Programmable Gate Arrayの略、つまり“現場で書き換えることができる論理回路の多数配列”です。定義としては、論理回路の設計を誤ったとしても、ハードウェア言語を使ってユーザが「その場」で「即座に」修正できるデバイスということです。昨今のFPGAのトレンドは、CPUコアを内蔵した「SoC FPGA」と変しています。

(コラム)FPGA入門

※VerilogとVHDLについて

Verilog(IEEE 1364として標準化)は、元は電子回路シミュレーションを実行するシミュレータでした。ソフトウェアプログラミング言語であるC言語やPascalに文法が似ていて、デジタル回路のレジスタ転送レベルの設計および検証によく使われます。一方のVHDL(IEEE/IECにより標準化)は、FPGAのほかにASICなどの設計にも使われます。

※RTLコーディングについて

主にFPGAデバイスメーカー(Xilinx社=半導体メーカー、Intel社=半導体素子メーカー)などのFPGAを動作させるために、論理回路をハードウェア記述言語(Hardware Discription Language; HDL)で設計・記述する手法のことです。C言語は聞きなれた言語だと思いますが、ハードウェア記述言語とは主にVerilogや、VHDL言語のことを示します。

★次回

次回は、「タイミングエラー」についてお話しようと思います。

<記者プロフィール>

ザミ

2002年から約15年間FPGA開発業務に従事。

その後、海外ベンダーのFPGAボード販売/FAEを担当している。

趣味はブラックバス釣り。フィッシュオン王禅寺でニジマス70匹/3Hゲットして浮かれ気分中。

個別相談も承っております。下記よりお申し込みください。