COLUMN

[FPGA設計のためのちょっとしたこだわり] 組み込みエンジニアなら知っておきたいRTLコーディングの基本

KUMICOをご覧の皆さまこんにちは!

[FPGA設計のためのちょっとしたこだわり] と題しまして、前回は“仕様書作成”工程のこだわりについてお話致しました。

さて、今回も“初めてFPGA設計とFPGA開発をします!”という新人エンジニアさんに対して、RTLコーディング工程の、私のちょっとしたこだわりや、予め気を付けた方がいいよ、という内容をお話ししようと思います。プログラミング初心者の方にもわかりやすい入門的な内容になっていますので、技術者の方はぜひ参考にしてみてください。

関連ソリューション

RTLコーディングはFPGAを動作させるためのプログラム

RTLコーディングとは、主にFPGAデバイスメーカー(Xilinx社=半導体メーカー、Intel社=半導体素子メーカー)などのFPGAを動作させるために、論理回路をハードウェア記述言語(Hardware Discription Language; HDL)で設計・記述する手法のことです。

C言語は聞きなれた言語だと思いますが、ハードウェア記述言語とは主にVerilogや、VHDL言語のことを示します。

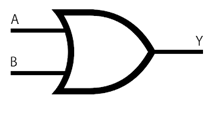

Verilogでコーディングすると、以下の記述になります。

assign Y= A | B;

FPGA設計において、このような論理回路や、F/F(フリップフロップ)をハードウェア記述言語によって実現することをRTLコーディングと言います。

Verilog、VHDL何が違うの?どちらを使えばいいの?という疑問がわきますが、どちらもさほど違いはありません。

FPGAの設計を学ぶ時、私は、まずVHDLを覚え、その後Verilogを覚えることになりましたが、基本的に大した違いはないのでVerilogも3日ほどで覚えることができました。とりあえずどちらかを覚えておけば大丈夫です。

私の経験上、Verilogは意外と抽象的な記述でも大丈夫で、画像系のプロジェクトでよく使用されております。

VHDLはきっちり記述しなくてはダメで、通信系のプロジェクトで使用されている印象があります。

「Verilogは抽象的でOK」「VHDLはきっちりでないとNG」というふうに何となく覚えておくといいでしょう。

FPGAの設計では、どちらを使用しなければならない等の明確なルールはありません。プロジェクトリーダーの趣味でどちらの言語を使用するか決まることもあります。

検証工程でテストベンチ(検証のための仮想的環境)を作成するとき、Verilogを拡張したSystemVerilogという言語も用いることがあるので、どちらかというとVerilogを先に学ぶことをお勧めします。

FPGA設計でRTLコーディングする前に決めておこう

①コーディングのパターンを決める

FPGA設計にあたり、まずはVerilog 、VHDLどちらを使用するかを決めます。

プロジェクト内で統一するのはもちろんですが、自分たちが作成する論理回路以外に、サードパーティが提供する“IP“というものを活用することもあります。

“IP”とは、例えばSDXC、UARTなど、ある機能を動かすための論理回路がすでにコーディングされており、そのIPを活用すれば、わざわざ自分達で膨大な工数をかけて、その機能をコーディングしなくて済みます。それらのIPがどちらの言語で作られているかも、具体的に設計に入る前に調査しておきましょう。

要は、プロジェクト内でVerilogとVHDLがミックスされないようにするのが鉄則です。

②コーディングルールを決める

プロジェクト内、もしくは会社単位でコーディングルールを決めている会社があります。

人によってコーディングスタイルは様々です。ルールに従って実装を行うことにより、記述内容の統一化、可読性の向上、バグが潜むような記述を防ぐなど、プロジェクトとして品質を向上することができます。

例えば、TABを使用してはダメ、信号名の命名規則、コメントを入れる場所、禁止される記述、非同期回路の記述方法、などさまざまなルールがある場合がありますので、具体的に設計に入る前にコーディングルールを確認してから作業を始めましょう。

FPGA設計におけるRTLコーディングのこだわり

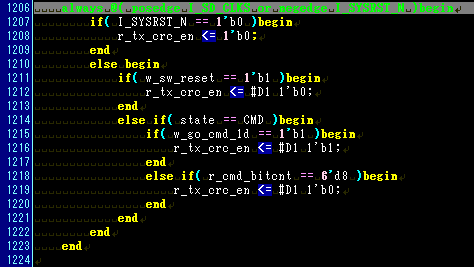

以下は、条件があるF/F(フリップフロップ)です。

①事前の単語登録で入力ミスを阻止

always、if、begin、endなど決まった単語があります。エディターにこれらの単語と色を割り当てて登録しておけば、記述ミスも防げるし、見やすいのです。皆様もどんどん登録しましょう。※登録しすぎるとカラフルになりすぎて不評です・・

②TABは使わない

TABを使用せず、スペースを使用しましょう。人によっては、エディターのTABの長さ(カラム)設定がまちまちです。自分が4カラムのTABで記述したとしても、1カラムの設定の人が、あなたのファイルを開くと見た目がガラッと変わってしまいます。エディターの設定に左右されないようにTABを使用せず、スペースを使用しましょう。私は半角スペースを4個使用してif分のネストを調整しています。

ミスやエラーはあって当たり前!入念な最終チェックを

さて、FPGA設計におけるRTLコーディングのフェーズが終わりました。

以下の点を注意して見直ししましょう。

①各行で無駄なスペースがないか。無駄なスペースが大量にあると汚く見えるので削除しましょう。

②コーディングルールに沿った記述になっているか。

③RTLの信号名や回路が、仕様書のタイミングチャートやブロック図と同じになっていること。仕様書とRTLが異なっていた場合、どちらが正解なのか分からなくなりますよね。もちろん仕様書が正解です!もし仕様書が間違っていた場合は、仕様書を修正+レビューをして、その仕様書に合わせてRTLをコーディングしなければなりません。

④RTLチェックツールで文法チェック、CDC(非同期)チェックをしましょう。RTLコーディングが終わったとしても、必ず文法間違いや非同期回路の記述ミスなど、さまざまなミスが潜んでいます。シミュレーションツールや、合成ツールでワーニング確認しても全てのミスを取り除くことはできません。RTLチェックツールは、Lint、Starc、CDCなどのルールに違反する部分を指摘してくれます。また、違反している個所を理解することにより、コーディング技術の向上にも繋がるので、必ずRTLチェックツールを実施して下さい。

次回

今回は「RTLコーディング」について、ちょっとしたこだわりや、注意すべき点をお話ししました。

一つでも役立つ内容があったら嬉しいです。

次回は、「シミュレーション」についてお話しようと思います。

※FPGAについて

FPGAとは、Field Programmable Gate Arrayの略、つまり“現場で書き換えることができる論理回路の多数配列”です。定義としては、論理回路の設計を誤ったとしても、ハードウェア言語を使ってユーザが「その場」で「即座に」修正できるデバイスということです。

FPGA入門はこちらから。

※VerilogとVHDLについて

Verilog(IEEE 1364として標準化)は、元は電子回路シミュレーションを実行するシミュレータでした。ソフトウェアプログラミング言語であるC言語やPascalに文法が似ていて、デジタル回路のレジスタ転送レベルの設計および検証によく使われます。一方のVHDL(IEEE/IECにより標準化)は、FPGAのほかにASICなどの設計にも使われます。

<記者プロフィール>

ザミ

2002年から約15年間FPGA開発業務に従事。

その後、海外ベンダーのFPGAボード販売/FAEを担当している。

趣味はブラックバス釣り。相模湖で6匹釣ゲットして浮かれ気分中。

個別相談も承っております。下記よりお申し込みください。