COLUMN

ASIC(特定用途向け集積回路)の設計・開発コラム

ASIC(Application Specific Integrated Circuit)とは、特定用途に向けて複数機能の回路をひとまとめにした半導体集積回路の総称で、エーシックと呼ばれています。ASICがつくられた経緯としては、機密となる回路構成を隠し、デバイス同士の接続箇所を減らす、さらに量産時と実装面積にかかるコストを低減させる目的がありました。特徴として高性能、コンパクトに作成ができる、製造時のコストの削減などがあげられます。

よくFPGA(Field Programmable Gate Array)やASSP(Application Specific Standard Product)と比較されます。ASIC (Application Specific Integrated Circuit)はFPGAと同様ハードウェア言語を用いて開発されますが、プログラマブルではないため論理回路の変更ができません。

ASICは、単機能ICおよび高性能演算用ICを除くほとんどの半導体製品を擁していて、その存在も多種多様。一般的にはデジタル回路が知られていますが、アナログ回路のみのものもあります。

種類は大きく分けて、ゼロから論理回路を設計するフルカスタムICと、基本的な回路や機能ブロックなどを組み合わせて設計するセミカスタムICがあります。セミカスタムICには、基本的な論理回路を敷き詰めた半完成品を用意し、回路間の配線を指定することで機能を実装する「ゲートアレイ(gate array)」方式や、ある程度まとまった機能を実装した部品化された回路(セル)を組み合わせていく「スタンダードセル」方式、両者の特徴を合わせた「エンベデッドアレイ(embedded array)」方式などがあります。一般的にはセミカスタムのASICが多くなりす。

ASICは家電製品や産業製品、高速処理が要求される通信機器、複合機やカメラの画像処理ほか、コンピュータシステム(CPU用の汎用チップセットや汎用標準バス制御など)などさまざまな電気製品に搭載(実装)されています。最近では、データ マイニングやGoogle社のTPUで有名な機械学習専用プロセッサでASICという用語を耳にする機会もあるかと思います。

今回のコラムでは、そんな半導体集積回路「ASIC」の設計・開発のプロセスと概要を紹介したいと思います。

ASICの設計と開発

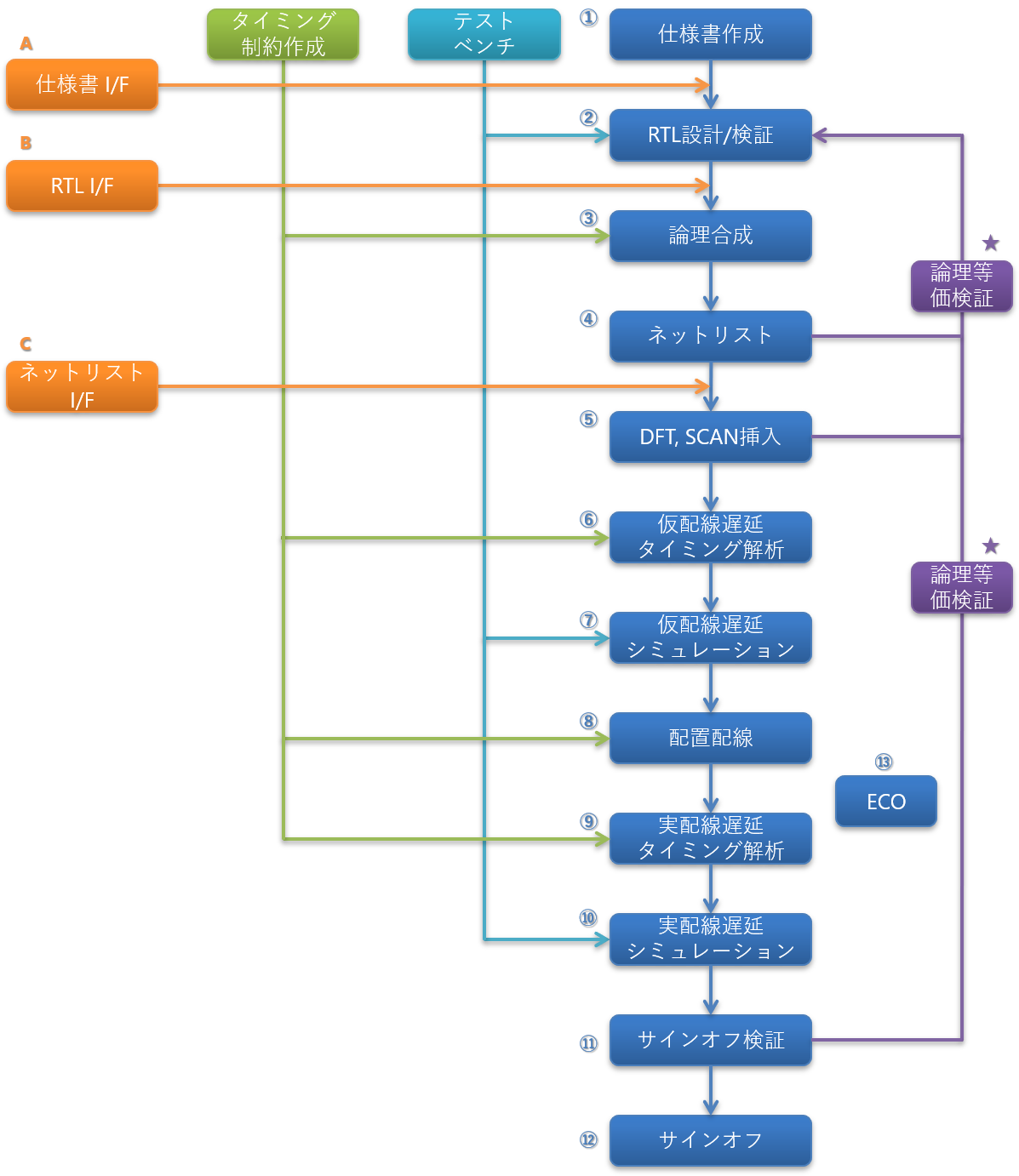

ASICの設計・開発フローをまとめると、以下のようになります。

① 仕様書作成

組み込みシステムの設計・開発は、まず要求仕様を検討し、仕様書を作ることから始まります。ASIC (Application Specific Integrated Circuit)の設計・開発のフローも同様です。

特定用途向け集積回路(ASIC)設計の仕様書のフォーマットや書き方などは各社ルールがあると思いますが、『[FPGA開発工程のちょっとしたこだわり] 仕様書作成』のページにて情報を投稿していますので、興味があればリンク先へ移動してみてください。

A) エーシック設計・開発側からの視点でお話しすると、この仕様書を受け取り、RTL設計から請け負うことを「仕様書I/F」と呼びます。お分かりの通り、RTLの記述は仕様書を元に行うことになりますので、仕様書の作成は非常に重要になります。

② RTL設計/検証

昔の半導体は論理回路記号を組み合わせ、回路図ベースで設計していましたが、現在ではverilog HDLやVHDLと呼ばれるハードウェア記述言語によってソフトウェアプログラミングのように記述し、設計するのが一般的です。

書き方としては、STARCのスタイルガイドに従う、信号やモジュール、ポートやインスタンス名などの命名規則に従うなど、各々のルールがあると思います。技術的な内容以外で筆者個人的に重要だと思うのは、

・インデント等を付けて見やすいようにする(一貫性が大事)

・ファイルヘッダに必要な情報を残す(回路名、機能名、作成者、作成日など)

・可読性を向上させるコメントを記載。英語で記載(parameterの説明など)

などであり、誰もが見やすく理解できることが大切です。

昔は変更履歴などもコメントで記載していましたが、どうしてもコメント行が増えてしまいますので、変更履歴管理ツールなどをうまく使うとよいでしょう。

B) お客様からRTLを受け取って開発を請け負うことをRTL I/Fと呼びます。具体的な機能、技術を知られたくない部分がある場合は暗号化されたRTLでリリースできますし、資産の流用も可能になるので、長年の筆者の経験としてRTL I/Fが一番いいと思います。

③ 論理合成

論理合成とは、LSIに適用するためRTL記述の回路から論理ゲートレベルのネットリストを作成することです。代表的なツールはSynopsys社のDesign CompilerやCadence社のRTL Compilerが一般的です。ただゲートレベルに合成するのではなく、後の配置配線時にタイミングが収束しやすいように考慮して合成する必要があります。そこで入力ファイルとして使用するのがSDCファイルと呼ばれるものです。SDCファイルには、

・クロック制約(各クロックの定義、周波数、Duty、Setup/Holdマージン)

・クロック間の制約(False Path、Multicycle Path)

・ACタイミング制約

など、制約を記載します。この制約は配置配線後のタイミング解析時と同じものを使用するのが望ましいですが、仮配線負荷にてあまりにも厳しい制約を与えてしまったり、ACタイミング制約を入れてしまうと、余計なバッファ等が挿入され、回路規模が大きくなってしまう場合があります。したがって、各種制約は別々のファイルで作成し、各工程にて必要なファイルを入力すると効率的です。

④ ネットリスト

論理合成後のゲートレベルの回路です。論理合成時に論理的な変更が入っていないかどうか、RTLと論理等価検証をする必要があります。Synopsys社のFormalityやCadence社のConformal LECが代表的なツールです。開発フロー(★)にあるように、各工程後にRTLと論理等価検証をすることが理想です。しかしながら、最近の開発では回路規模も大きく複雑になることから、工程が進むにつれて論理等価検証が難しく、かつ実行に膨大な時間がかるため現実的ではありません。現在では各工程にてチェックポイントを設け、論理等価検証を行うのが通常のフローとなっています。

RTL ⇔ ネットリスト ⇔ DFT挿入後 ⇔ 配置配線後 ⇔ サインオフネットリスト

C) お客様からネットリストを受け取って開発を請け負うことをネットリスト I/Fと呼びます。ネットリストであれば機能や回路情報が読み取れず、RTLをリリースする必要もないため資産の流出も防ぐことができます。しかしながら、論理合成などに使用するEDAツールは高価なものが多く、タイミングを考慮して合成をする必要もあるため、あまりネットリストI/Fで請け負うことはありません。

⑤ DFT、SCAN挿入

DFTとはDesign For Testabilityの略で、テスト容易化設計のことです。ASIC(Application Specific Integrated Circuit)出荷時のテストでは、回路の機能ではなく内部の物理的な故障が無いかを確認することになります。ちなみにFPGAではメーカーが出荷時にテストを行っているため、これらのテストは必要ありません。

テスト容易化のためASIC内部の状態が外部端子から観測しやすいようにテスト回路の挿入やテストパタンの作成が必要になります。これらを効率よくする技術がDFT、SCANです。主なテストは以下の3つです。

・メモリBIST

その名の通り、メモリ故障を検出するテストです。BISTとはBuilt-In Self-Testの略で、テストパタンを作成する回路とテスト結果を判定する回路を挿入し、内部で自己テストが出来る機能です。テストパタンの作成も必要が無く、テストピンも少なくて済むのでコスト削減が可能なテスト方法です。

・JTAG(バウンダリスキャン)

バウンダリスキャンはI/Oの故障を検出するテストです。JTAGの機能を使うことで内部回路に影響を与えることなくテスト可能です。

・SCANテスト

内部の組み合わせ回路の故障を検出するテストです。ここでは詳細は割愛いたしますが、FFをSCAN FFに置き換えシフトレジスタを構成し、外部I/Oから制御・観測を行うことで組み合わせ回路を動作させ、故障を検出することが可能となります。テストパタンはATPG(automatic test pattern generator)と呼ばれるツールで作成可能です。

⑥ 仮配線遅延タイミング解析

この段階では仮配線遅延での解析となるため、タイミング制約がきちんと作成出来ているかや、クリティカルパスやファンアウトの確認が主なポイントとなります。

配置配線時にタイミング的な問題がないか、特別にケアすべき大きなファンアウトはないか、すべてのタイミングパスを解析出来ているかを主に確認します。余計なセルが多段に入ってしまい、タイミングの収束性を悪化させるようなパスがある場合、論理合成時の制約や設定にを見直すことで解消することがあります。この辺りはツールの癖や経験がものを言うところになりますが、おかしいなと思うことがあれば、前工程に戻って確認することで解決する場合があります。

⑦ 仮配線遅延シミュレーション

前述したように、各工程で論理等価検証をしているかと思いますが、この工程でシミュレーションによる論理検証を行います。RTLから組み合わせ回路になったことや、DFTを挿入したことによる影響がないかを確認します。

また、DFTで挿入した各テスト回路の検証やSCANの検出率の確認を行い、正しくテスト回路が挿入されているか、機能しているか確認します。

⑧ 配置配線

筆者はフロントエンドの技術者であったため、レイアウトツールにはあまり詳しくありませんが、配置配線を行う上で必要な制約、またタイミングを収束させるためのポイントがありますので、経験をもとにお話しします。

特に重要だと考えるのは2点、フロアプランとクロック設計です。

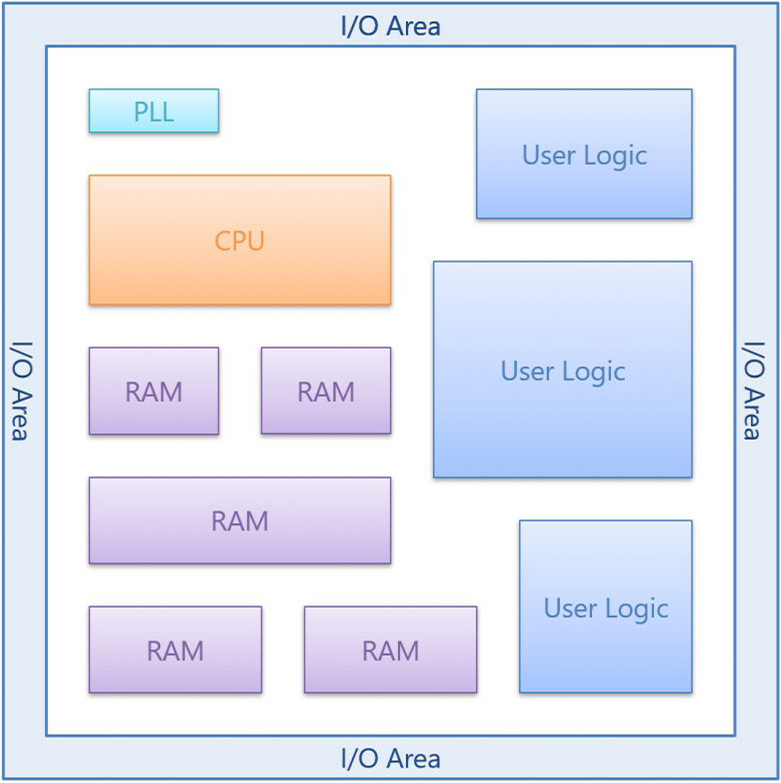

・フロアプラン

先に大きさや形状が決まっているRAMやPLLのマクロを配置し、そのあとにUser Logicをどのように配置するか決めていきます。ここでのポイントは、クリティカルパスをどう配置するかということです。ある特定のFF間のSetupタイミングが厳しいのであれば、そのパスを固めて配置する、ACタイミングであれば対象のセルをI/Oの近くに配置する、などの工夫が必要になります。

・クロック設計

もう一つ大切になってくるのはクロック設計で、どのようにクロックを配線するかになります。

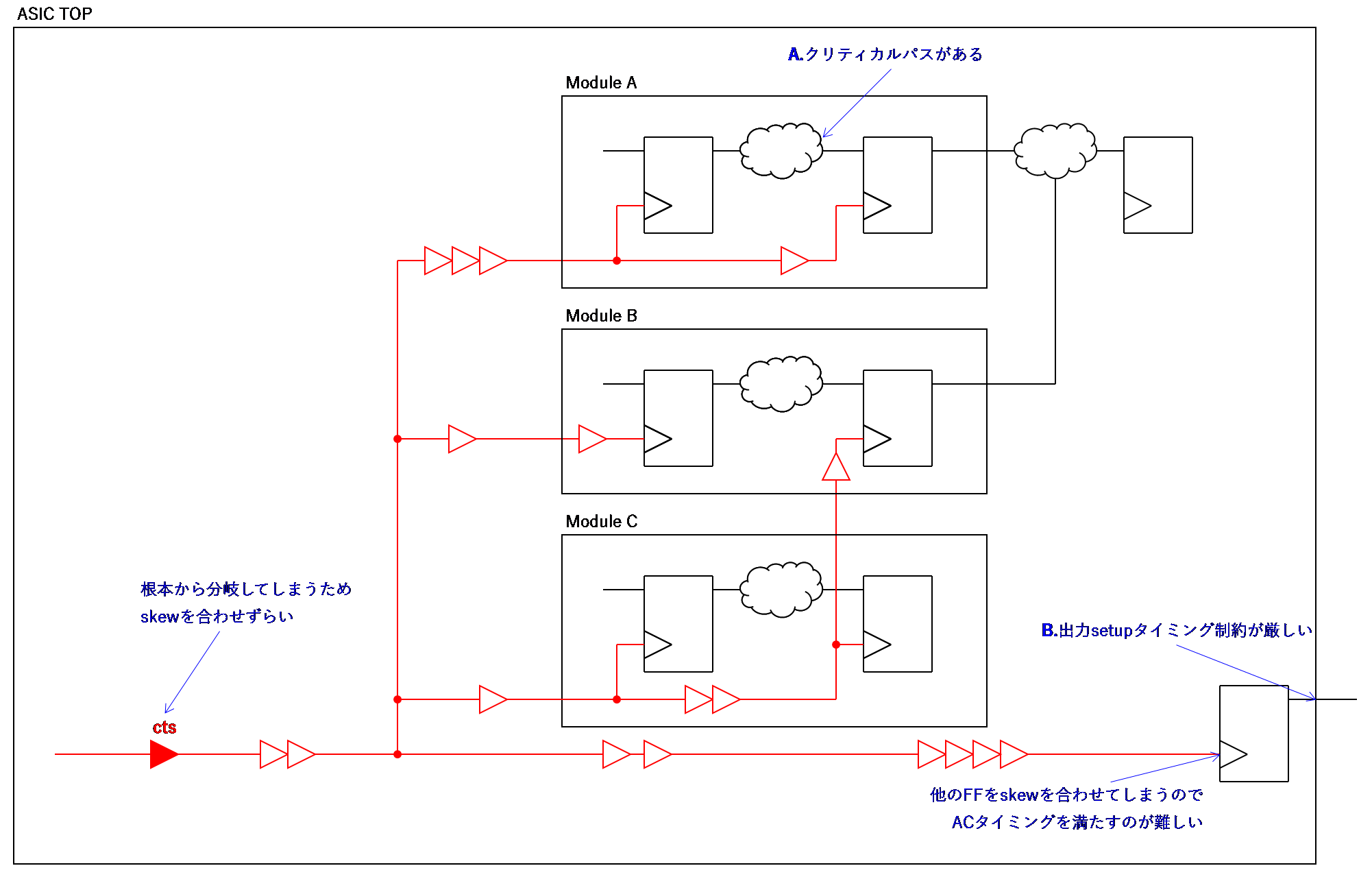

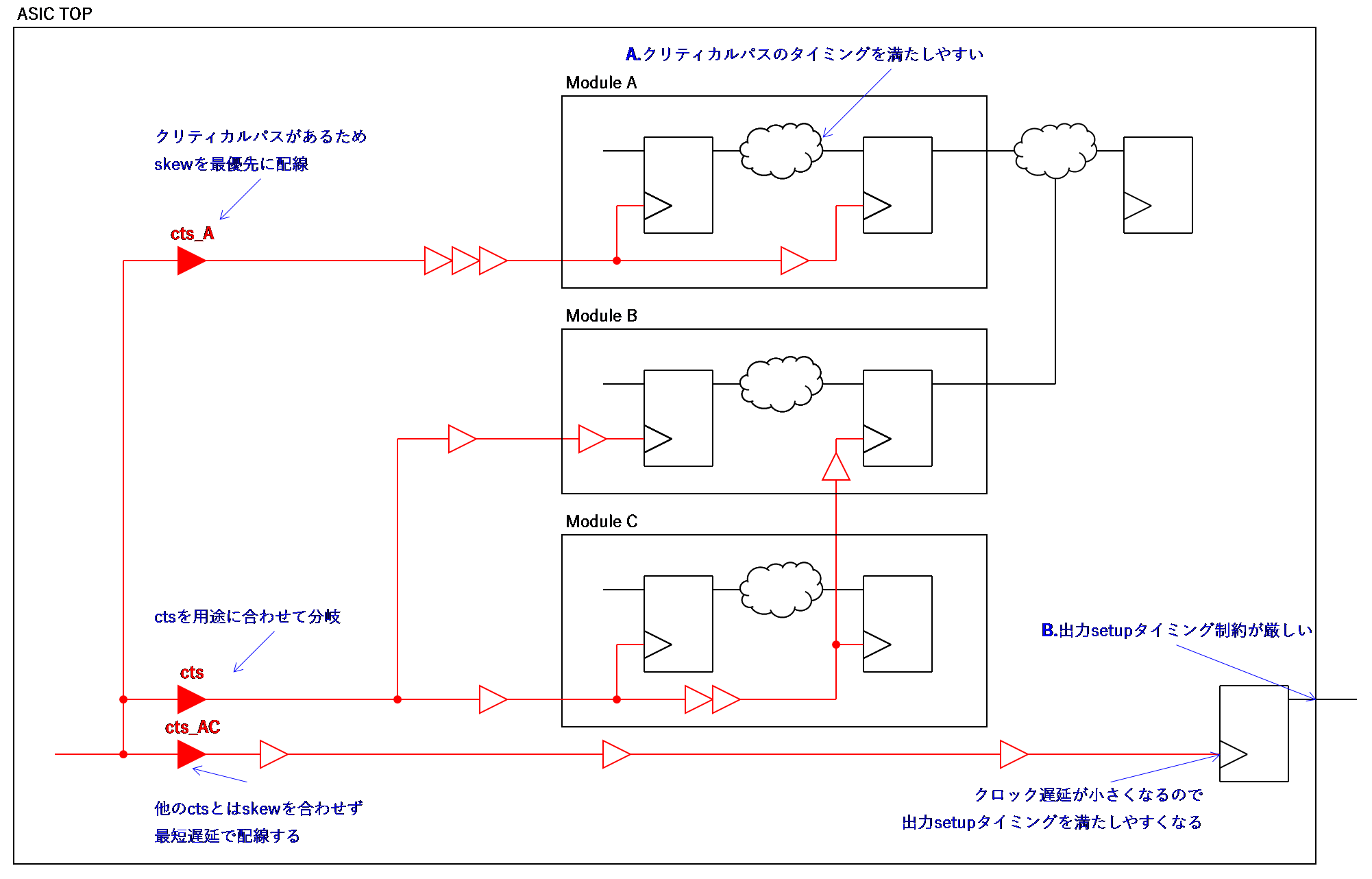

例を挙げて説明しましょう。以下は、クロック設計を意識しない配線と意識した配線の図です。

今回の例は内部のクリティカルパスとACタイミングについてです。

A. 内部クリティカルパス

ご存知のように、クロックの理想配線は遅延が少なくskewが0になることです。skewが大きいとhold対策用のバッファなど余計なセルを入れる必要が出てきます。またsetupのクリティカルパスにも大きく影響します。

この場合、クリティカルパスとなるブロックを先述のフロアプランで固めるように配置し、このブロックに専用のctsを用いることで、接続先のFF数が少なくなり、skewを小さくすることが可能になります。その結果、クリティカルパスのタイミングを満たしやすくなるのです。

また、他のctsで配線したクロック間のタイミングは、ctsの根元で遅延を調節することで対応可能となります。

B. ACタイミング対策

今回は、出力AC setupタイミング対策に関する例です。

出力AC setupタイミング制約が厳しい場合、いかに遅延を小さくしてI/Oまでデータを出力するかがポイントとなります。この場合も、フロアプランにてACタイミング対象のFFをI/Oに近づけ、ctsをAC専用に分け最短遅延にてクロックを配線することでタイミングを満たしやすくなります。

出力クロックの遅延を大きくするという方法もあるのですが、遅延を大きくするということはバッファなどのセルが多段に挿入されることになり、min条件とmax条件の遅延差が大きくなります。すると、setupタイミングは満たせるがholdタイミングは満たせないといったことが起き、おすすめできません。セル数をいかに少なくするかが基本的な考え方です。結果として、タイミング設計の容易化や面積縮小、省電力化につながり、コストも下がります。

こうした対策をすることでタイミング設計の容易化につながり、配置配線後の工程が楽になります。

論理合成時から配置配線をイメージしてクロック設計を検討しておくことが大切です。

⑨ 実配線遅延タイミング解析

基本的には、⑥で行った解析を配置配線後のデータを利用して行うことになります。初回の配置配線後では、クリティカルパスの対策結果やクロック設計など、タイミング収束の為に行った対策が正しいか、さらにその他の対策をするべきかを判断することが大切になります。特に問題が無ければこのまま進みますが、収束性が難しい場合、配置配線時の制約を見直すことで改善出来ないか、クリティカルパスが複雑な論理となっている場合、RTLを書き換えて合成することでシンプルな回路構成にならないか等、前の工程をさかのぼって見ることが必要です。これにより、タイミングの収束性が良くなり、ロジックセル数が減り、コストが下がることがあります。そのため、初回のタイミング解析は検討する事項が多く、とても大切な工程となります。

⑩ 実配線遅延シミュレーション

次に、配置配線後のタイミングデータを使用して論理の検証を行います。各工程間にて論理等価検証を行っていると思いますが、論理が正しいかシミュレーションを行い、DFTにて挿入した各テストが正しく動作しているかを確認します。

また、タイミング解析で発見できなかったパスやグリッチがある場合、このシミュレーション中に発見することも可能です。出荷テスト時に使用するテストパタンを選別する必要もあるため、各遅延条件にてシミュレーションを行うことが重要です。

⑪サインオフ検証

大まかに分類すると⑨実配線遅延タイミング解析や⑪実配線遅延シミュレーションもサインオフ検証の一部になりますが、ここではその他に必要となる検証を行います。

・DRC/LVSなどの各種フィジカル検証

・パワー解析(電流密度による電圧降下など)

・出荷テストパタンの選別と検出率の確認(出荷テスト時にすべての回路を動作させることが出来るか)

近年ではテクノロジーの微細化により、様々な確認事項が増えてきておりますが、基本的にはこのようなテストを行いサインオフとなります。

⑫ サインオフ

上記すべての検証を完全に終えると、サインオフ、チップの製造工程へ進みます。

チップの製造工程はウェーハプロセス、パッケージング、検証となりますが、当記事では割愛させていただきます。

⑬ ECO(Engineering Change Order)

実際の設計において、上記すべての工程で仕様変更やバグ修正等で回路を手直しする可能性があり、このような修正は通常ECOと呼ばれます。ECOはRTL記述に対するものであれば比較的簡単ですが、ネットリスト、特にDFTやSCAN挿入後のネットリストに対するものは、極めて困難な場合があります。

以上がASIC開発工程(サインオフまで)となります。

ユーザーがASICに求めるのは、システム処理要求を送ってから短い時間で処理結果が出力されることです。そのために重要になってくるのが、設計手法と設計ツールなのです。また、取り扱う論理ゲート数の増大にともない、高い性能を持つ各種設計ツールや高いレベルでの論理設計も重要度を増していくことになります。

ASICは、フォトマスク(電子部品の回路パターンを転写するための原板)が高価ゆえに少量生産に不向きである、すべてを個別設計するため人件費がかかる、納期が長いなど、さまざまな課題があります。しかし一方で、標準ロジックICやFPGA、プログラマブルロジックデバイスなどと比べると消費電力の低減や動作速度の向上、単価が安いなどといったメリットもあります。

本コラムやエーシックに関すること、富士ソフトが扱うメーカー製品その他に関することは気軽にお問い合わせください。

個別相談も承っております。下記よりお申し込みください。