COLUMN

ソフトエンジニア向けFGPAでOpenCL™を始めるっ!~OpenCL™サンプルデザインの動作確認~

今回は、第4回 いよいよ!OpenCL™サンプルデザインの動作確認です。

FPGAでOpenCL™を始めるのってソフトウェアエンジニアにとっては

技術的に敷居が高いと感じている方向けに、

Intel®のFPGAを利用して数回にわたりコラムを掲載させて頂きます。

「OpenCL™って何?」という方は、こちらをどうぞ。

FPGAの利点も記載されておりますのでご参照ください。

下記は、前回までのおさらいです。

第3回:OpenCL™サンプルデザインのコンパイル

第2回:インストールと環境構築

第1回:ハードとソフトの準備

前回までに用意した下記のファイルやフォルダを用意してください。

■LinuxKernel/ドライバ・モジュールの準備

・コンパイル済みカーネル

フォルダロケーション:<kernel_sourcode_tree>/arch/arm/boot/

ファイル名:zImage

・ドライバ・モジュール

フォルダロケーション:<kernel_sourcode_tree>/../modules/lib/modules/4.9.78-ltsi/

■OpenCL(TM)ランタイムの準備

フォルダロケーション:<opencl_rte_download_folder>

フォルダ名:aocl-rte-18.0.0-614.arm32

■ boardtestとhello_worldのビルド結果

フォルダロケーション:

<home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/boardtest

<home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/hello_wrold

■SDCardイメージファイル

第1回でダウンロードしたTERASIC社のDE10-Nano KitのサイトのResourcesタブからDE10-Nano OpenCL BSP (.tar.gz)に含まれているde10_nano_opencl.zipファイル

事前に、下記に示すLinux Kernelのコンフィグ内容を追加して再度コンパイルを行ってください。

また、それに伴いLinux Kernelのコンパイル後にLinux Kernelのドライバ・モジュールとOpenCL™ランタイムのコンパイルを行ってください。

お手間お掛け致しますm(_ _)m

Linux Kernelのコンフィグ方法、各コンパイル方法は、第2回:インストールと環境構築をご参照ください。

LinuxKernelのコンフィグを追加する部分のみを以下に示します。

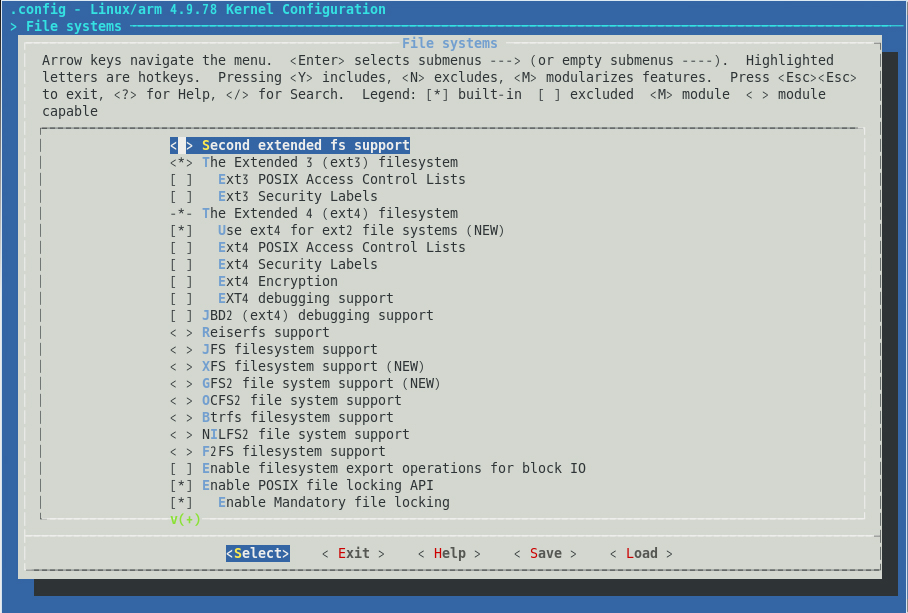

メニューコンフィグの画面から、File systemsを選択後、下記画面が表示されます。

Second extended fs supoortを↑↓キーで選択します。

スペースキー操作を行い、[ ] Second extended fs support の状態にしてください。

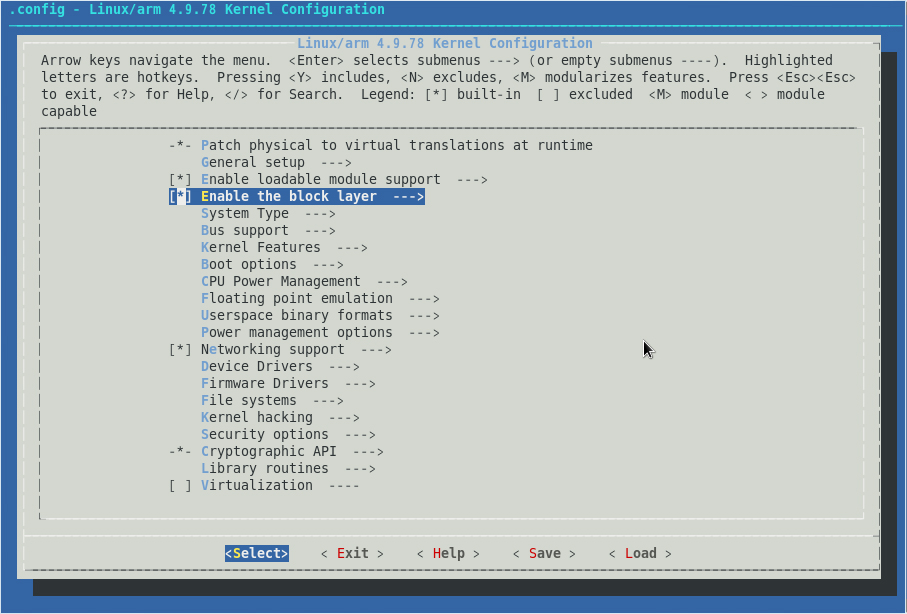

メニューコンフィグのTOPの画面にEnable the block layerメニューが追加されているので、↑↓キーを操作して選択してリターンキーを押します。

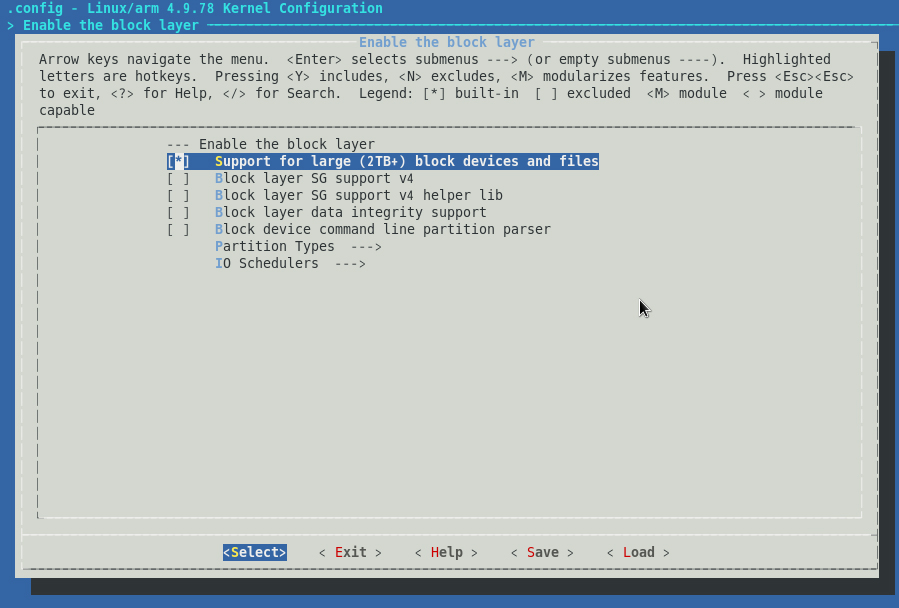

↑↓キーを操作して Support for large (2TB+) Block devices and filesを選択します。

スペースキーを押して[*]の状態にします。

←→キーを操作し<Save>を選択してリターンキーを押し、.configureファイルの更新を行ってください。

その後、LinuxKernelのコンパイル、ドライバ・モジュールとOpenCL™ランタイムのコンパイルを実施してください。

(1)SDCardイメージファイルの解凍とSDCardへの書き込み

※書き込みは30分ぐらいかかります。

# cd ~

# source ./

# ./SoCEDSSetup-18.0.0.614-linux.run

# cd <home_folder>/intelFPGA_std/18.0/ embedded/

# source ./embedded_command_shall.sh

~~

~~

# cd <DE10-Nano-OpenCL_BSP_1.0.tar.gz_download_folder>/

# tar xzvf DE10-Nano-OpenCL_BSP_1.0.tar.gz

# cd de10_nano

# unzip de10_nano_opencl.zip

(2) SDCardイメージファイルの書き込み

SDCardをUSBアダプタ等を利用して、PCへ接続します。

接続後、アサインされたドライブ・マウントポイントを確認します。

※環境により、ドライブ番号やマウントポイントは異なります。

自動でマウントされない場合は、コマンドにより500M側をマウントしてください。

また、マウント時はvfatパーティションのため、相当のオプションを設定してください。

# lsblk

~~

~~

sdd 8:48 0 7.3T 0 disk

└─sdd1 8:49 0 7.3T 0 part

sde 8:64 1 14.9G 0 disk

├─sde1 8:65 1 500M 0 part /media/5BDF-419D

├─sde2 8:66 1 1G 0 part /media/847f4797-311c-4286-8370-9d5573b201d7

└─sde3 8:67 1 1M 0 part

sr0 11:0 1 1024M 0 rom

~~

~~

#

(3)DeviceTreeファイルの更新

まず、DeviceTreeファイルを更新するために、SDCardの中にあるDeviceTreeファイルを取り出します。

※SDCardの500Mのパーティションが/media/5BDF-419Dにマウントされた場合の例です。

# su

パスワード:

# cd /media/5BDF-419D

# cp /media/5BDF-419D/socfpga.dtb \(<=バックスラッシュ)

<DE10-Nano-OpenCL_BSP_1.0.tar.gz_download_folder>/ de10_nano

# exit

# cd <DE10-Nano-OpenCL_BSP_1.0.tar.gz_download_folder>/ de10_nano

dtbファイルからdtsファイルへ変換を行い、dtsファイルの編集を行います。

※今回はgeditエディタを利用しています。

# dtc -I dtb -O des -o socfpga.dts socfpga.dtb

# gedit socfpga.dts

socfpga.dtsファイルに以下を追記して保存します。

~~

~~

dwmmc0@ff704000 {

compatible = "altr,socfpga-dw-mshc";

reg = <0xff704000 0x1000>;

interrupts = <0x0 0x8b 0x4>;

fifo-depth = <0x400>;

#address-cells = <0x1>;

#size-cells = <0x0>;

clocks = <0x20 0x21>;

clock-names = "biu", "ciu";

num-slots = <0x1>;

supports-highspeed;

broken-cd;

altr,dw-mshc-ciu-div = <0x3>;

altr,dw-mshc-sdr-timing = <0x0 0x3>;

bus-width = <4>; <=追記

cap-sd-highspeed; <=追記

status = "okay"; <=追記

slot@0 {

cd-gpios = <0x22 0x12 0x0>;

reg = <0x0>;

bus-width = <0x4>;

};

};

~~

~~

~~

~~

fpgamgr@0xff706000 {

compatible = "altr,fpga-mgr-1.0", "altr,fpga-mgr";

transport = "mmio";

reg = <0xff706000 0x1000 0xffb90000 0x1000>;

interrupts = <0x0 0xaf 0x4>; <=追記

reg-names = "axi_slave0", "axi_slave1"; <=追記

clocks = <0x3>; <=追記

};

fpgabridge@0 {

compatible = "altr,socfpga-hps2fpga-bridge";

label = "hps2fpga";

clocks = <0x3>; <=追記

reset-names = "hps2fpga"; <=追記

resets = <&rst_mgr 96>; <=追記

};

fpgabridge@1 {

compatible = "altr,socfpga-lwhps2fpga-bridge";

label = "lwhps2fpga";

clocks = <0x3>; <=追記

reset-names = "lwhps2fpga"; <=追記

resets = <&rst_mgr 97>; <=追記

};

~~

~~

rst_mgr: rstmgr@ffd05000 { <=変更

compatible = "altr,rst-mgr", "syscon";

reg = <0xffd05000 0x1000>;

#reset-cells = <1>; <=追記

};

~~

~~

dtbファイルを生成します。

# dtc -I dts -O deb -o socfpga.new.dtb socfpga.dts

dtbファイルをSDCardへ書き込みます。

# su

パスワード:

# cd <DE10-Nano-OpenCL_BSP_1.0.tar.gz_download_folder>/ de10_nano

# cp -rf socfpga.new.dtb /media/5BDF-419D/

(4)rbfファイルの更新

rbfファイルをSDCardへ書き込みます。

# cd <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/boardtest

# cp -rf top.rbf /media/5BDF-419D/opencl.rbf

(5)LinuxKernelイメージファイルの更新

zImageファイルをSDCardへ書き込みます。

# cd <kernel_sourcode_tree>/arch/arm/boot/

# cp -rf zImage /media/5BDF-419D/

(6)LinuxKernelドライバ・モジュールの更新

SDCardへLinuxKernelのドライバ・モジュールを書き込みます。

# cd <linux_kernel_download_folder>

# cd ../

# tar czvf modules.tar.gz ./modules

# cp modules.tar.gz /media/847f4797-311c-4286-8370-9d5573b201d7/lib/modules

# cd /media/847f4797-311c-4286-8370-9d5573b201d7/lib/modules

# tar xzvf modules.tar.gz

# mv modules/lib/modules/4.9.78-ltsi ./

# rm -rf modules/

# rm -rf modules.tar.gz

# ls

# 4.5.0+ 4.9.78-ltsi

#

(7)OpenCL™ラインタイムの更新

# cd <opencl_rte_download_folder>

# tar czvf aocl-rte-18.0.0-614.arm32.build.tar.gz aocl-rte-18.0.0-614.arm32/

# cp czvf aocl-rte-18.0.0-614.arm32.build.tar.gz /media/847f4797-311c-4286-8370-9d5573b201d7/home/root/

# cd /media/847f4797-311c-4286-8370-9d5573b201d7/home/root/

# tar xzvf aocl-rte-18.0.0-614.arm32.build.tar.gz

ライブラリ名称の下位互換の対応

これはあまりお勧めする方法では無いのですが、ライブラリの名称が変わっています。

本来は、別のファイルで修正を行うべきなのですが、ここでは昔のライブラリ名に対応するためにファイル名で対応をおこないます。

# cd aocl-rte-18.0.0-614.arm32/board/c5soc/arm32/lib/

# cp libintel_soc32_mmd.so libalterammdpcie.so

(8)OpenCL™環境変数スクリプトの更新

export INTELFPGAOCLSDKROOT=/home/root/aocl-rte-18.0.0-614.arm32

export AOCL_BOARD_PACKAGE_ROOT=/home/root/aocl-rte-18.0.0-614.arm32/board/c5soc

export PATH=$PATH:/home/root/aocl-rte-18.0.0-614.arm32/bin:

export LD_LIBRARY_PATH=/home/root/aocl-rte-18.0.0-614.arm32/host/arm32/lib:$LD_LIBRARY_PATH

export LD_LIBRARY_PATH=/home/root/aocl-rte-18.0.0-614.arm32/board/c5soc/arm32/lib:$LD_LIBRARY_PATH

insmod /home/root/aocl-rte-18.0.0-614.arm32/board/c5soc /arm32/driver/aclsoc_drv.ko

init_opencl.shファイルを以下の内容で生成してください。

SDCardへinit_opencl.shを書き込みます。

# cp -rf init_opencl.sh /media/847f4797-311c-4286-8370-9d5573b201d7/home/root/

(9)OpenCL™サンプルデザインの更新

OpenCL™サンプルデザインをSDCardへ書き込みます。

#cd /media/847f4797-311c-4286-8370-9d5573b201d7/home/root

#mkdir exsamples

#cd exsamples

#mkdir boardtest

#cd boardtest

#cp <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/boardtest/device/boardtest.aocx ./

#cp <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/boardtest/boardtest_host ./

#cd ../

#mkdir hello_world

#cd hello_world

#cp <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/hello_wrold/device/hello_world.aocx ./

#cp <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/exsamples/hello_wrold/bin/hello_world ./

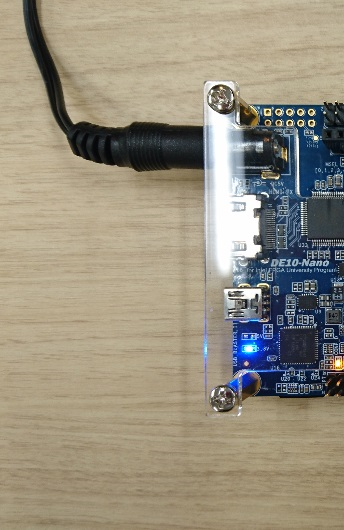

(10)DE10-Nanoの準備と起動

※DE10-Nanoの基板に「UART」とシルクが入っています。

PCのドライバのインストールが必要な場合は、適宜インストールを行います。

シリアルポートの設定は下記の設定です。

ボーレート:115200

データ:8bit

パリティ:none

ストップビット:1bit

フロー制御:none

改行コード設定:受信CR 送信CR

ローカルエコー:なし

ACアダプタとDE10-Nanoを接続後、コンセントと接続して電源を投入します。

暫く経つとターミナル画面に下記が表示されますので、ログイン名 「root」でログイン操作をします。

[ OK ] Started Update UTMP about System Runlevel Changes.

The Angstrom Distribution socfpga ttyS0

Angstrom v2014.12 - Kernel

socfpga login:

(11)OpenCL™の準備

OpenCL™ RTEを有効にするためにinit_opencl.shスクリプトを実行します。

root@socfpga:~# source ./init_opencl.sh

OpenCL™診断プログラムを実行します。

root@socfpga:~# aocl diagnose acl0

Verified that the kernel mode driver is installed on the host machine.

Using platform: Intel(R) FPGA SDK for OpenCL(TM)

Board vendor name: Intel(R) Corporation

Board name: de10_nano_sharedonly : Cyclone V SoC Development Kit

Buffer read/write test passed.

DIAGNOSTIC_PASSED

(12)サンプルデザインの実行

boardtestサンプルデザインを実行してみます。

root@socfpga:~# cd exsamples/boardtest

root@socfpga:~# ./boardtest_host

~~

~~

eprogramming device [0] with handle 1

sh: /sys/class/fpga-bridge/fpga2hps/enable: No such file or directory

sh: /sys/class/fpga-bridge/hps2fpga/enable: No such file or directory

sh: /sys/class/fpga-bridge/lwhps2fpga/enable: No such file or directory

Couldn't open FPGA status from /sys/class/fpga/fpga0/status!

sh: /sys/class/fpga-bridge/fpga2hps/enable: No such file or directory

sh: /sys/class/fpga-bridge/hps2fpga/enable: No such file or directory

sh: /sys/class/fpga-bridge/lwhps2fpga/enable: No such file or directory

Reprogram FAILED

mmd program_device: Board reprogram failed

~~

~~

な、なんと、、、上記エラーにより失敗しています。

どうやらKernelバージョンが新しくなって?OpenCL™RTEが参照しているファイルが無くなっています!!

次回はこの回避方法を検討します。

※参考サイト:インテル® FPGAのサイト

(https://www.altera.co.jp/products/design-software/embedded-software-developers/opencl/overview.html)

※各ツールのライセンスや購入に関しては、代理店・メーカにお問い合わせください。

※本コラムは、弊社が実際に開発をした中での経験より構成しております。本内容に準じて実施した結果に生じるいかなる影響、損害に関して、責任の無いものといたします。本コラムで紹介しておりますツールについては、合法性、正確性、道徳性、最新性、適切性、著作権の許諾や有無など、その内容については、何らの責任を負うものではありません。また、当社は通知することなく当サイトに掲載した情報の訂正、修正、追加、中断、削除等をいつでも行うことができるものとします。コンテンツのご利用により、万一、ご利用者様に何らかの不都合や損害が発生したとしても、当社は何らの責任を負うものではありません。

個別相談も承っております。下記よりお申し込みください。