COLUMN

ソフトエンジニア向けFPGAでOpenCL™を始めるっ!~インストールと環境構築~

今回は、第2回 インストールと環境構築をしましょう。

FPGAでOpenCL™を始めるのってソフトウェアエンジニアにとって技術的に敷居が高いと感じている方向けに、

Intel®のFPGAを利用して数回にわたりコラムを掲載させて頂きます。

OpenCL™って何?って方は、KUMIKOの下記コラムをご参照ください。

また、FPGAの利点も記載されておりますのでご参照ください。

https://www.fsi-embedded.jp/kumico/column/118/

関連ソリューション

前回ダウンロードしたファイルは下記4種類ですね。

■インテル® SoC FPGA エンベデッド・デベロップメント・スイート スタンダードエディション 18.0

ファイル名:SoCEDSSetup-18.0.0.614-linux.run

■インテル® FPGA SDK for OpenCL™ スタンダードエディション 18.0

ファイル名:AOCL-18.0.0.614-linux.tar

■OpenCL™RTE(ランタイム環境)スタンダードエディション 18.0

ファイル名:aocl-rte-18.0.0-614.arm32.tgz

■TERASIC社のDE10-nanoのOpenCL™BSP

ファイル名:DE10-Nano_OpenCL_BSP_1.0.tar.gz

以降の手順でインストールを進めましょう!

※ /home/dnndev/がホームホルダの例として記載しています。

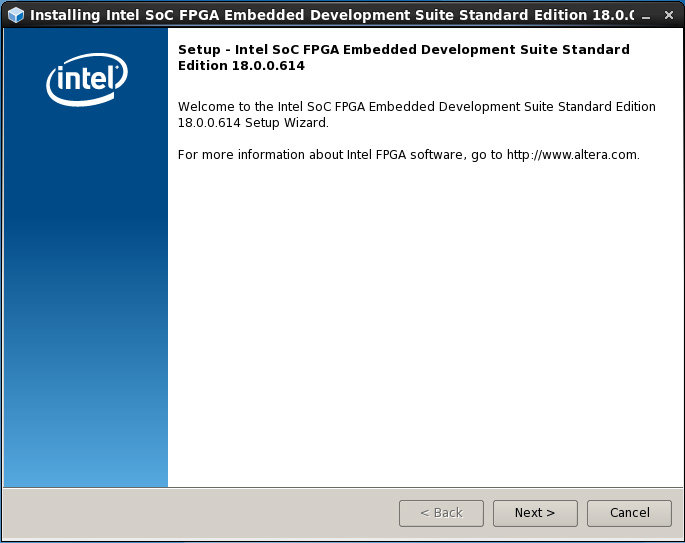

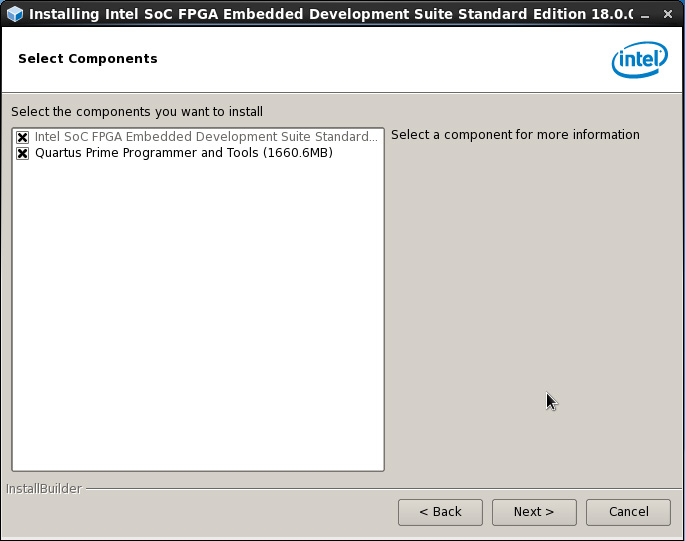

(1)インテル® SoC FPGA エンベデッド・デベロップメント・スイート スタンダードエディション 18.0のインストール

下記のコマンドをLinuxのターミナルから実行してインストールを開始します。

# chmod +x SoCEDSSetup-18.0.0.614-linux.run

# ./SoCEDSSetup-18.0.0.614-linux.run

Next >ボタンをクリックします。

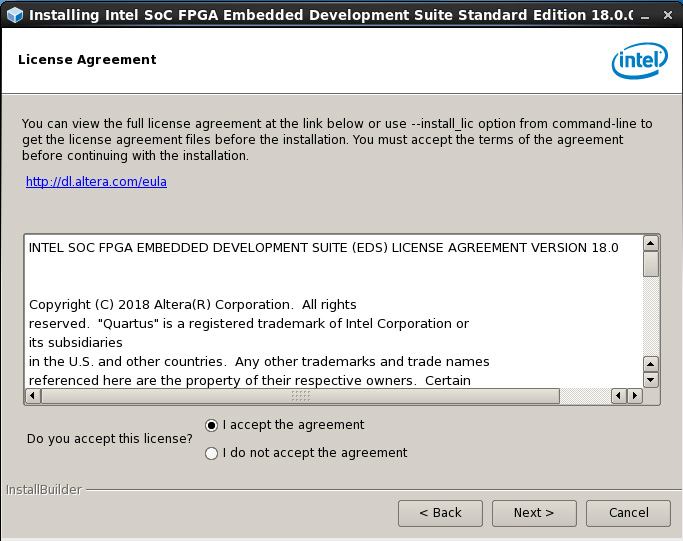

I accept the agreementを選択してNext >ボタンをクリックします。

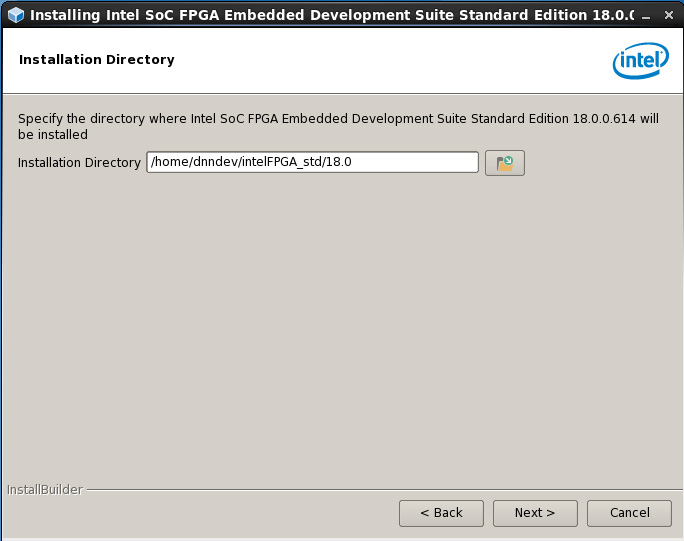

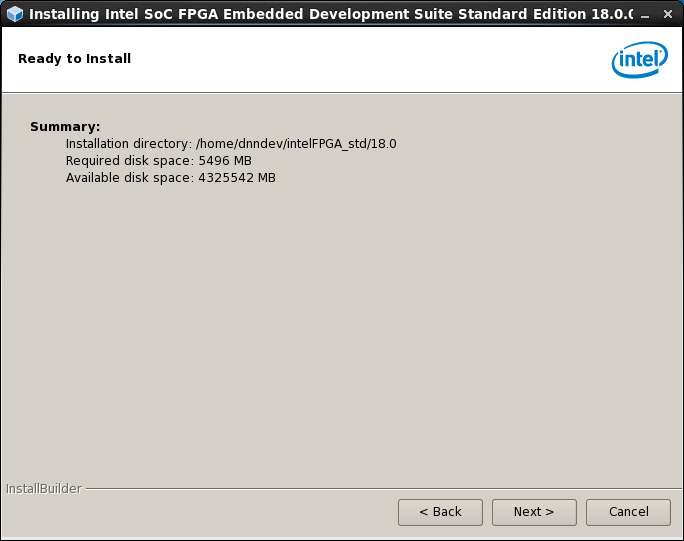

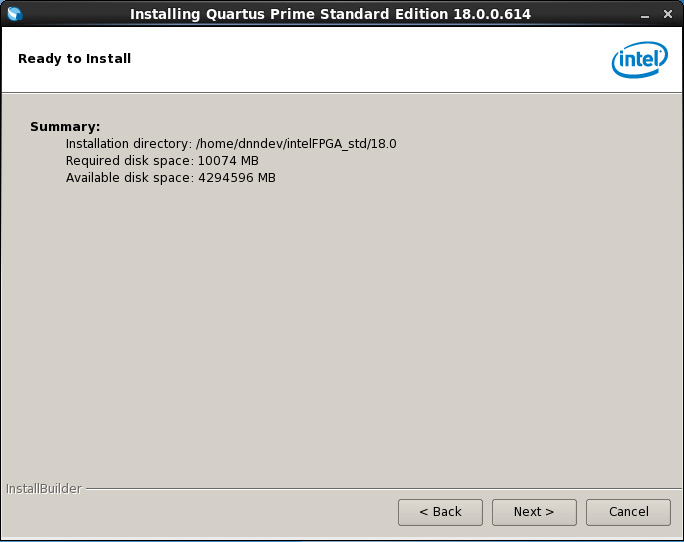

フォルダボタンをクリックして、ホームフォルダ配下(今回の例では/home/dnndev)にintelFPGA_std/18.0フォルダを作成して、インストール先に設定してください。

その後、Next >ボタンをクリックします。

Next >ボタンをクリックします。

Next >ボタンをクリックします。

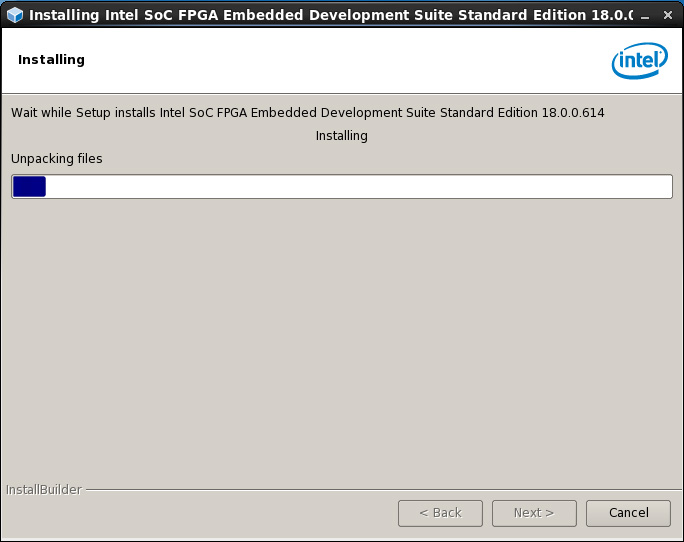

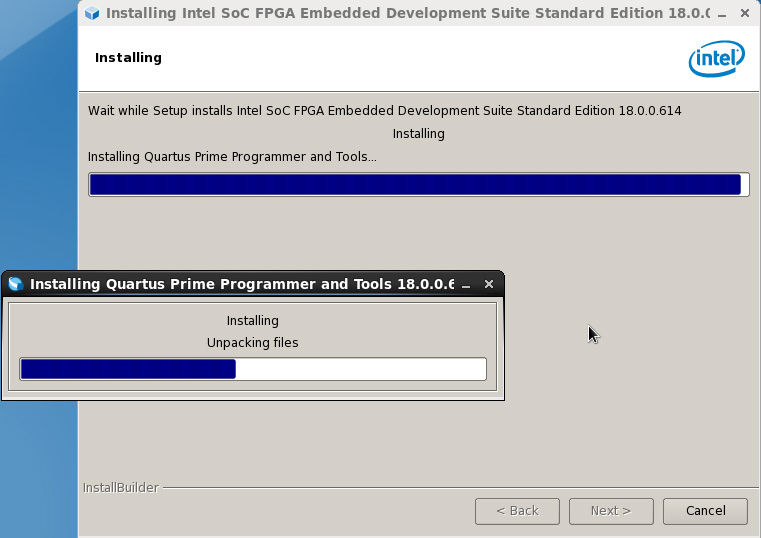

インストールが開始されます。

インストールが進んでいきます。

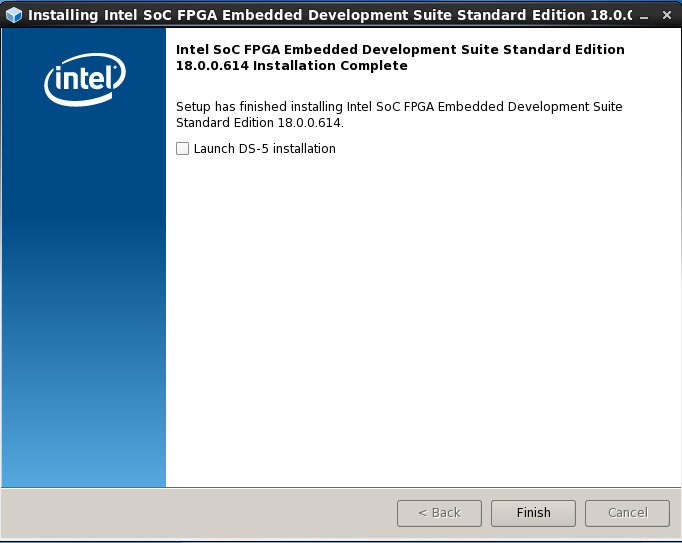

Launch DS-5 installationのチェックマークを外してからFinishボタンを押します。

この後LinuxのコマンドプロンプトからDS-5をインストールします。

Linuxのコマンドプロンプトより下記の手順によりDS-5をインストールしてください。

※ログインユーザをsudoersに事前に加えておいてください。

# cd /home/dnndev/intelFPGA_std/18.0/embedded/ds-5_installer

# sudo ./install.sh

Please answer with one of: ‘yes’ or ‘no/quit’

Do you agree to the above terms and conditions? yes ← yesを入力

Run installation platform requirement checks? [default: yes] ← リターンを入力

Where would you like to install to? [default: /usr/local/DS-5_v5.28.1] /home/dnndev/intelFPGA_std/18.0/embedded/ds-5 ← DS-5インストール先を入力

Please answer with one of: ‘yes/y’ or ‘no/n’

‘/home/dnndev/intelFPGA_std/18.0/embedded/ds-5’ does not exist, create? [default: yes] ← リターンを入力

— Installing to ‘/home/dnndev/intelFPGA_std/18.0/embedded/ds-5’ (This may take a while…)

Please answer with one of: ‘yes/y’ or ‘no/n’

Install desktop menu item additions? [default: yes] ← リターンを入力

….

….

Please answer with one of: ‘yes/y’ or ‘no/n’

Run post install setup scripts? [default: yes] ← リターンを入力

———————————–

Installation completed successfully

———————————–

To start using Arm DS-5 v5.28.1 either:

– Create a suite sub-shell using /home/dnndev/intelFPGA_std/18.0/embedded/ds-5/bin/suite_exec

– Launch GUI tools via their desktop menu entries

The Release notes for the product can be found here: file:///home/dnndev/intelFPGA_std/18.0/embedded/ds-5/sw/info/readme.html

=============================================

[dnndev@dnndev ds-5_installer]$

以上で、インテル® SoC FPGA エンベデッド・デベロップメント・スイート スタンダードエディション 18.0が完了です。

(2)インテル® FPGA SDK for OpenCL™ スタンダードエディション 18.0のインストール

下記のコマンドをLinuxのターミナルから実行してインストールを開始します。

# mkdir AOCL-18.0.0.614

# mv AOCL-18.0.0.614-linux.tar AOCL-18.0.0.614

# tar xvf AOCL-18.0.0.614-linux.tar

# ./setup.sh

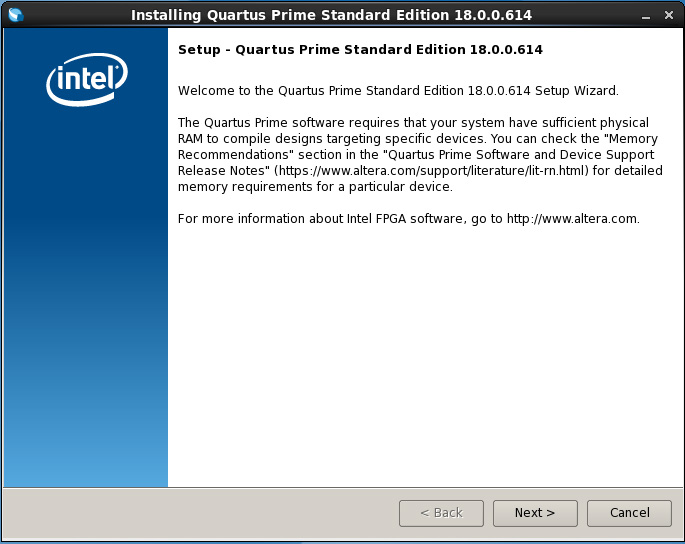

Next >ボタンをクリックします。

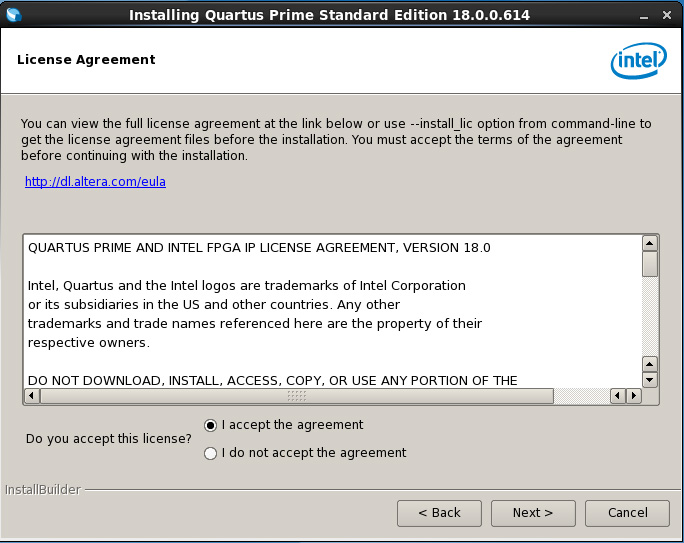

I accept the agreementを選択してNext >ボタンをクリックします。

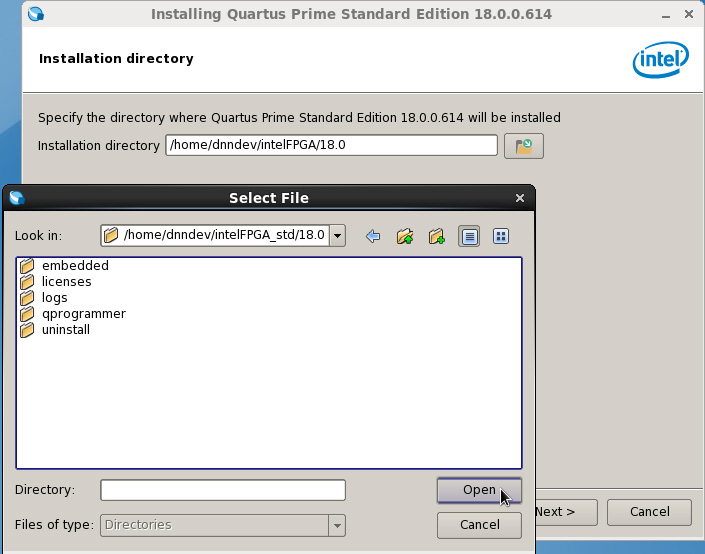

フォルダボタンをクリックして、先ほどインテル® SoC FPGA エンベデッド・デベロップメント・スイート スタンダードエディション 18.0をインストールした際に作成したフォルダを選択してOpenボタンを選択し、その後Next >ボタンを選択します。

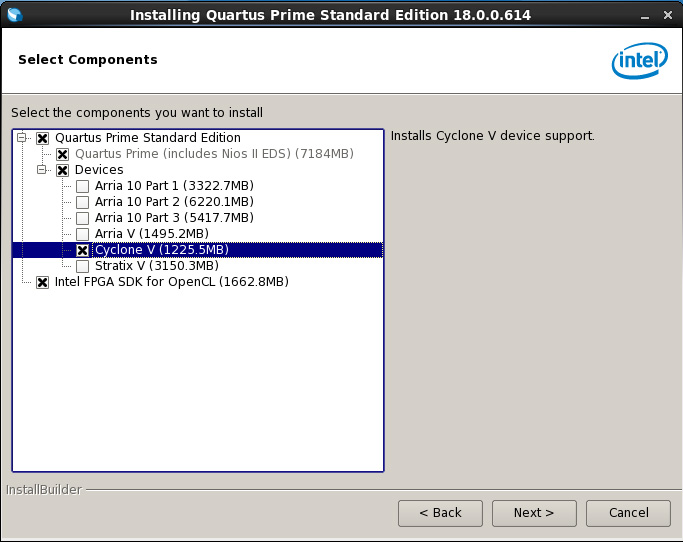

Devices TreeのCycloneV(1225.5MB)のみを選択します。

デフォルトでは、その他のデバイスも選択されているので、Xマークを外します。

その後、Next >ボタンを選択します。

Next >ボタンを選択します。

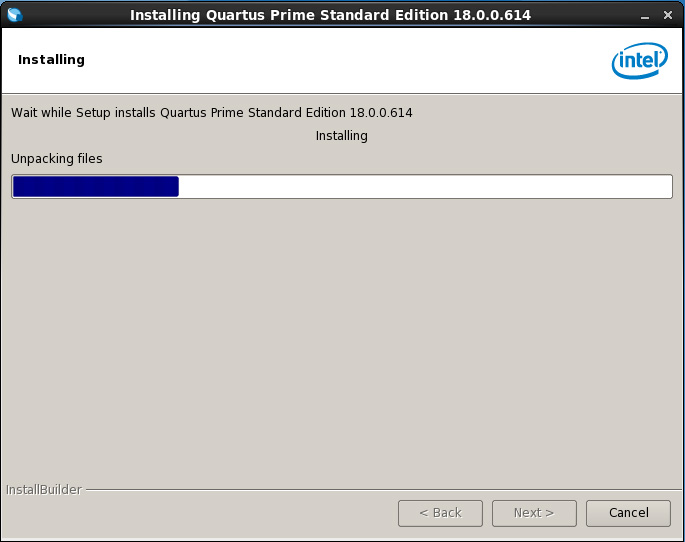

インストールが開始されます。

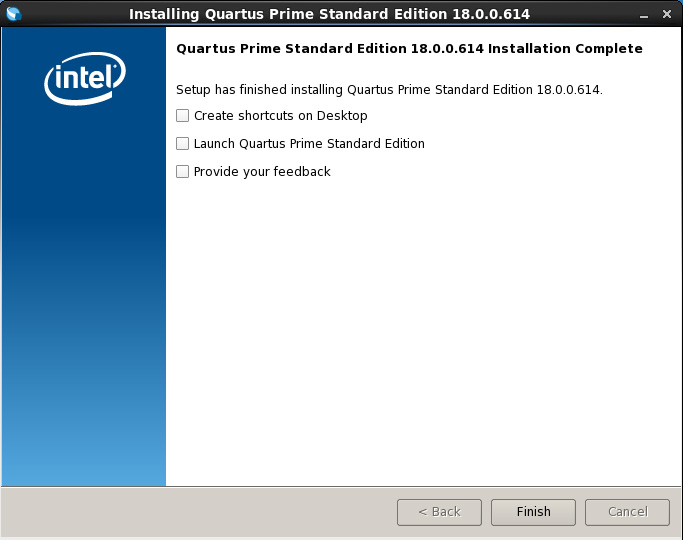

Create shortcuts on Destop

Launch Quartus Prime Standard Editionのマークを外して、Finishボタンをクリックします。

以上で、インテル® FPGA SDK for OpenCL™ スタンダードエディション 18.0のインストールが完了です。

(3)TERASIC社のDE10-nanoのOpenCL™BSPのインストール

下記のコマンドをLinuxのターミナルから実行してインストールを行います。

# cd

# tar xzvf DE10-Nano_OpenCL_BSP_1.0.tar.gz

# cd /home/dnndev/intelFPGA_std/18.0/hld/board

# mkidr terasic

# cd terasic

# cp -rf

以上で、DE10-nanoのOpenCL™BSPのインストールが完了です。

環境変数設定スクリプトを作る!

下記コマンドにより、環境変数設定スクリプトを作成します。

# cd ~

# vi .quartus18.0.0.std.de10-nano

export QUARTUS_VERSION_DIR=”/home/dnndev/intelFPGA_std/18.0″

export ALTERAOCLSDKROOT=”/home/dnndev/intelFPGA_std/18.0/hld”

export INTELFPGAOCLSDKROOT=”$QUARTUS_VERSION_DIR/hld”

export QSYS_ROOTDIR=”/home/dnndev/intelFPGA_std/18.0/qsys/bin”

export QUARTUS_ROOTDIR=”$QUARTUS_VERSION_DIR/quartus”

export QUARTUS_ROOTDIR_OVERRIDE=”$QUARTUS_ROOTDIR”

export SOPC_KIT_NIOS2=”$QUARTUS_VERSION_DIR/nios2eds”

export PATH=$QUARTUS_ROOTDIR/bin:$PATH

export PATH=$ALTERAOCLSDKROOT/bin:$PATH

export PATH=$PATH:$QUARTUS_VERSION_DIR/modelsim_ase/linux

export LD_LIBRARY_PATH=$ALTERAOCLSDKROOT/host/linux64/lib:$AOCL_BOARD_PACKAGE_ROOT/linux64/lib:$LD_LIBRARY_PATH

export INTELFPGAOCLSDKROOT=”$QUARTUS_VERSION_DIR/hld”

export QUARTUS_64BIT=1

export QUARTUS_DIR=”$QUARTUS_VERSION_DIR/quartus”

export AOCL_BOARD_PACKAGE_ROOT=”$QUARTUS_VERSION_DIR/hld/board/terasic/de10nano”

export LD_LIBRARY_PATH=$ALTERAOCLSDKROOT/linux64/lib

#vv installed ds5

export PATH=$PATH:$QUARTUS_ROOTDIR/bin:$QUARTUS_VERSION_DIR/embedded/ds-5/bin:$QUARTUS_VERSION_DIR/embedded/ds-5/sw/gcc/bin:$ALTERAOCLSDKROOT/bin:$ALTERAOCLSDKROOT/linux64/bin:

:wq

DE10-nanoのOpenCL™BSPをインテル® FPGA SDK for OpenCL™ 18.0化する!

DE10-nanoのOpenCL™BSPはインテル® FPGA SDK for OpenCL™ 18.0で生成されたものでは無いため、プロジェクトを18.0対応にします。

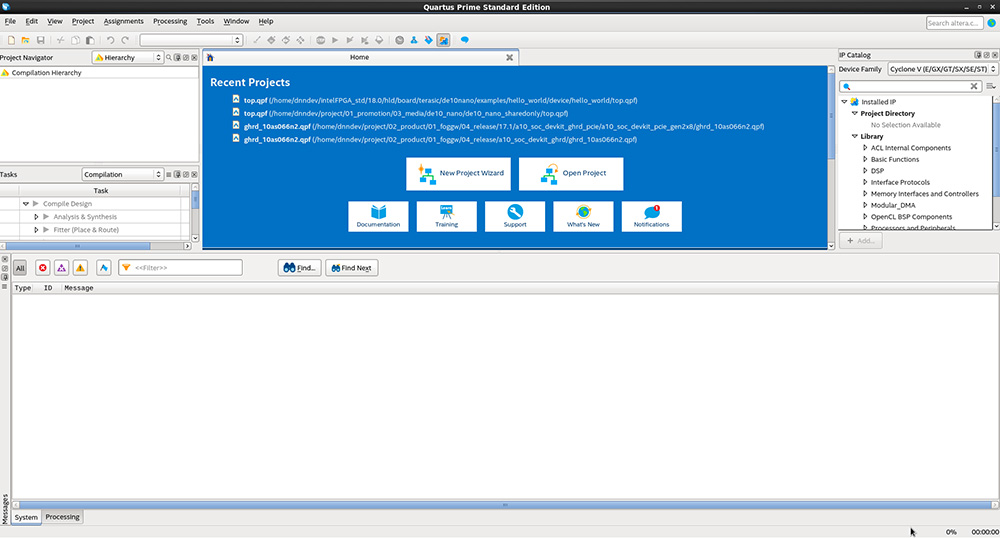

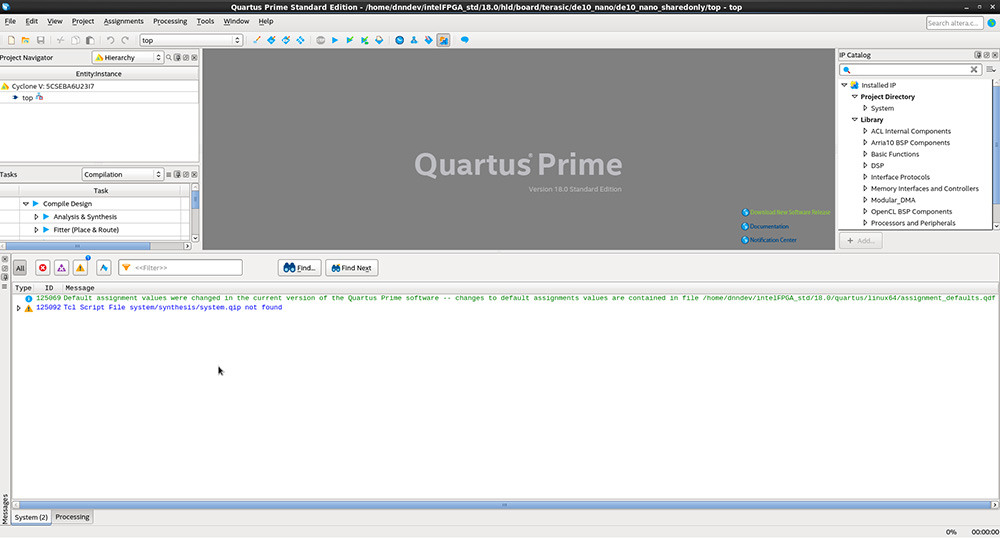

ターミナルよりquartusを起動します。

# cd ~

# source .quartus18.0.0.std.de10-nano

# quartus

※License Setup Requiredの画面が出てきた場合は、それに従ってください。

※ライセンスに関しましては、代理店又はメーカーまでお問い合わせください。

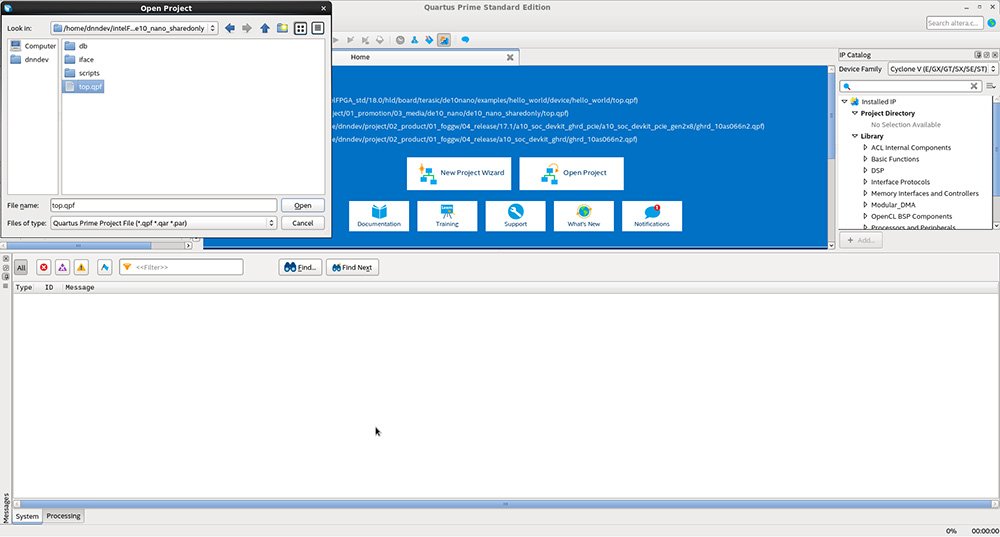

FileメニュのOpen Projectを選択します。

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10nano/top.qpfを開きます。

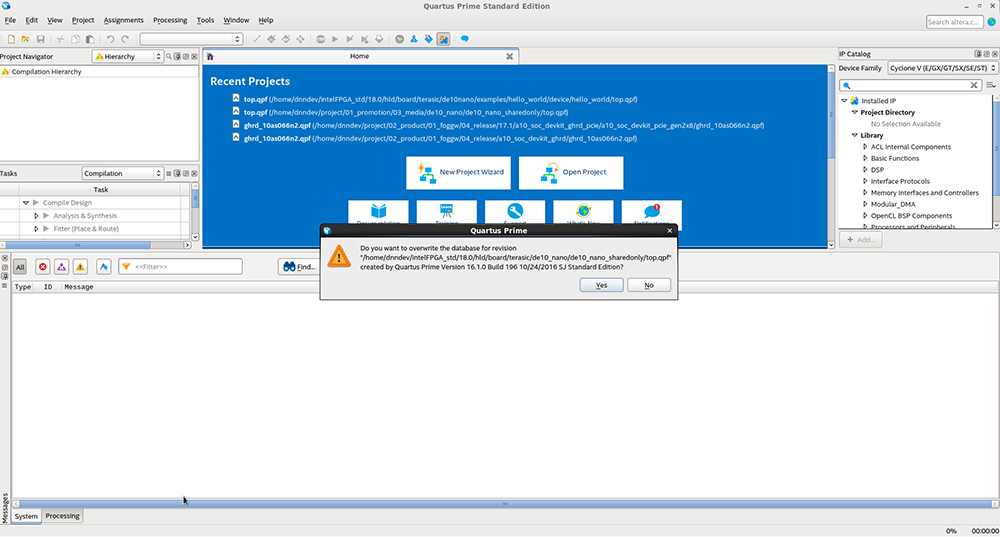

Yesボタンを選択します。

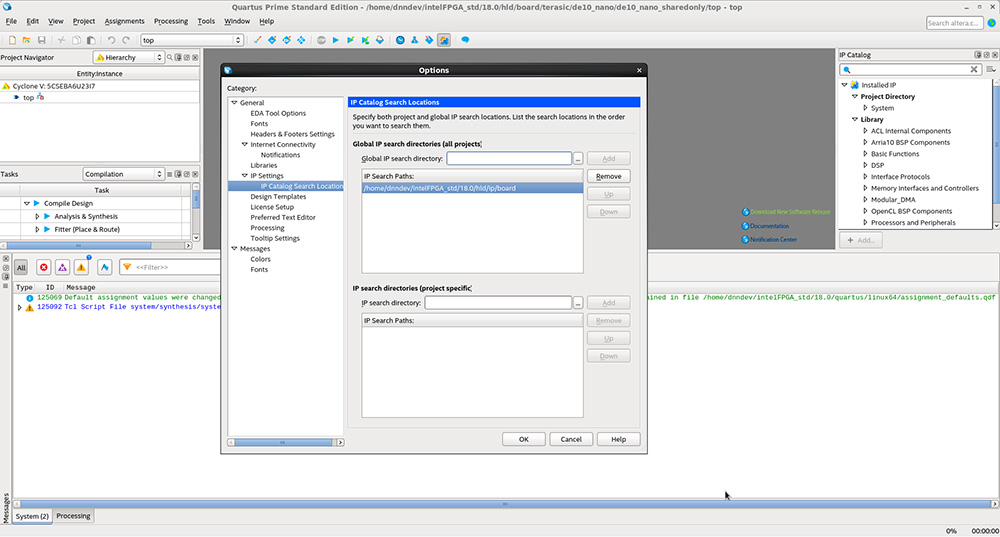

ToolsのOptions..を選択し、IP Catalog Serch Locationを選択します。

Global IP search directoryに、/home/dnndev/intelFPGA_std/18.0/hld/ip/boardを入力し、Addボタンを選択します。

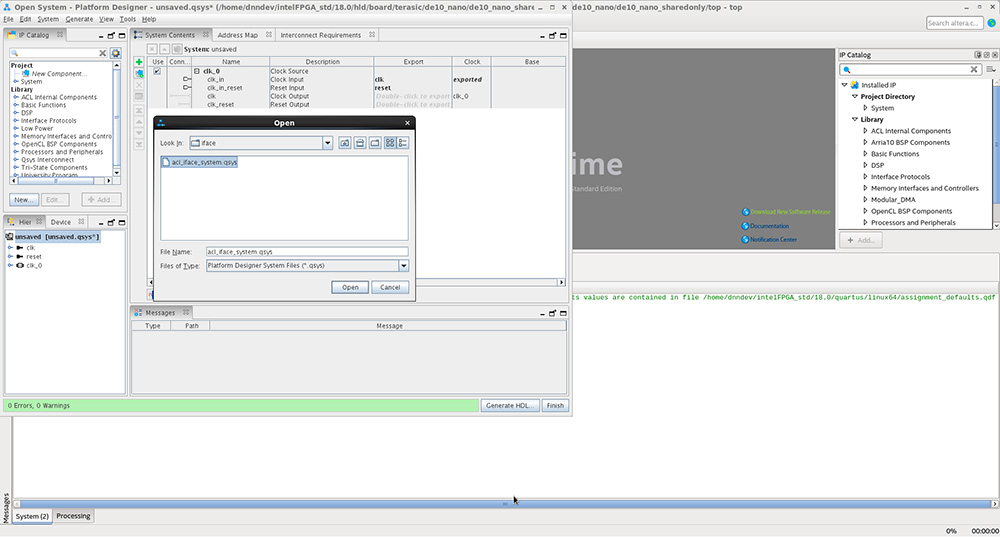

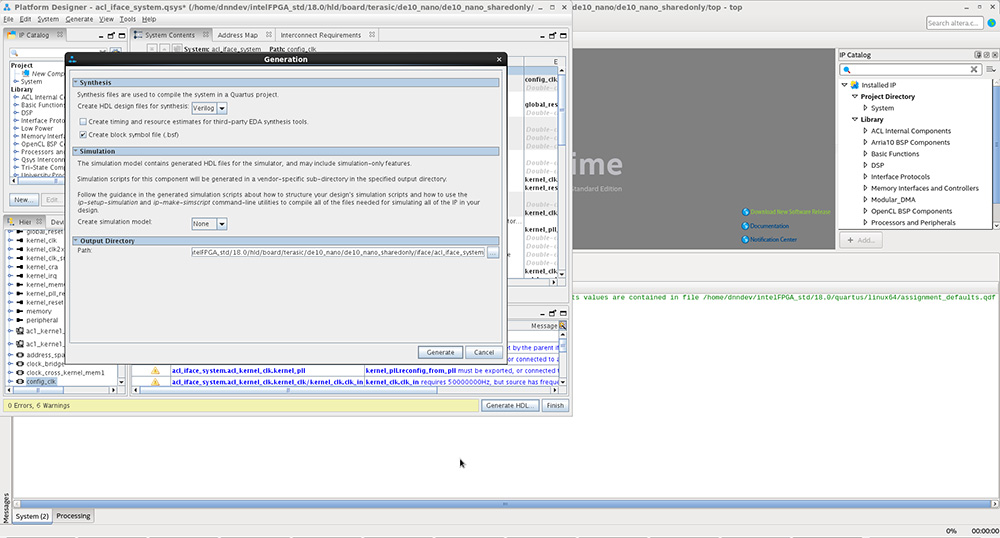

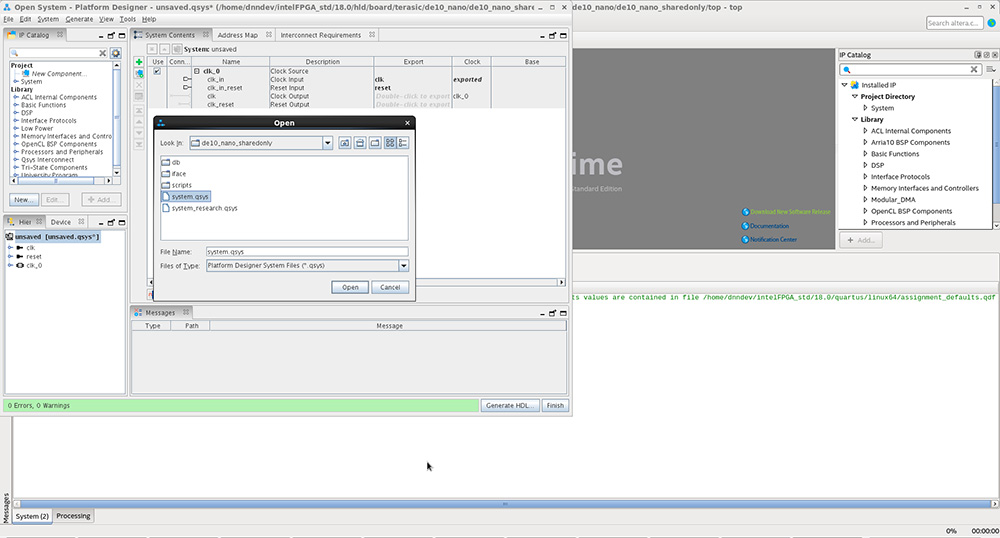

Tools->Platform Designerを選択し、PlatfromDesignerのFile->Open..

/home/dnndev/intelFPGA_std/18.0/hld/terasic/de10_nano/de10_nano_sharedonly/iface/acl_iface_system.qsysを選択し、Openボタンを選択します。

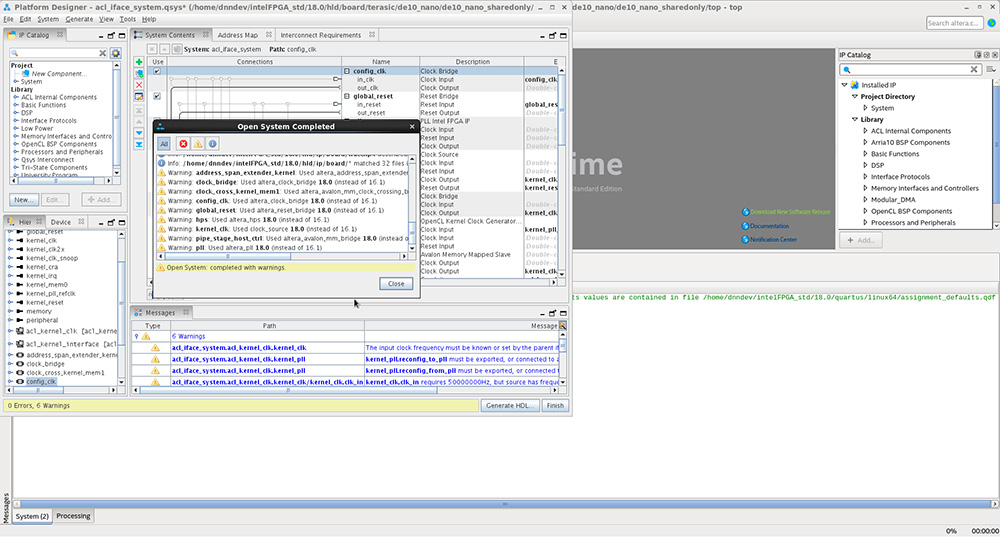

下記の様な画面に遷移して暫く待ちます。

Closeボタンを選択します。

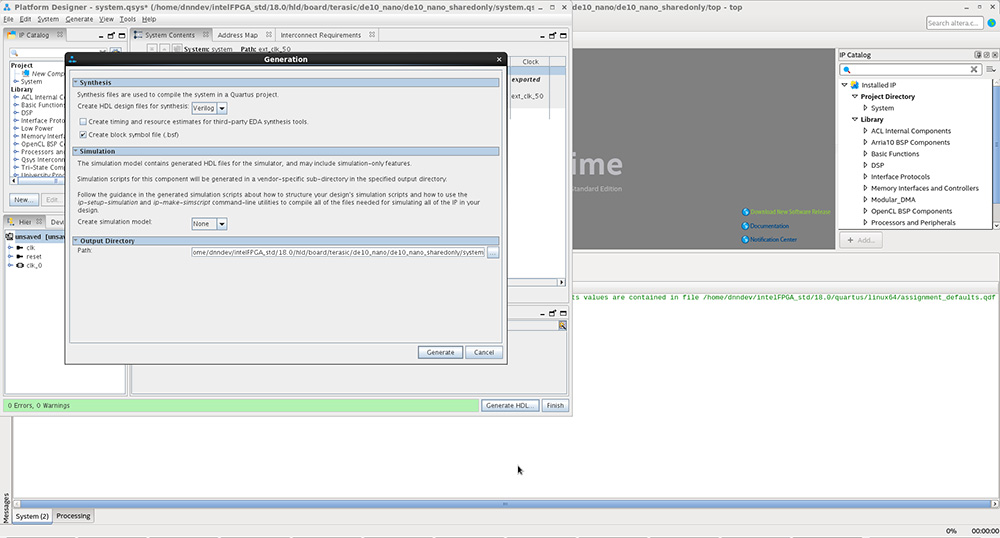

Generate HDL..ボタンを選択します。

Generation 画面の Generate ボタンを選択します。

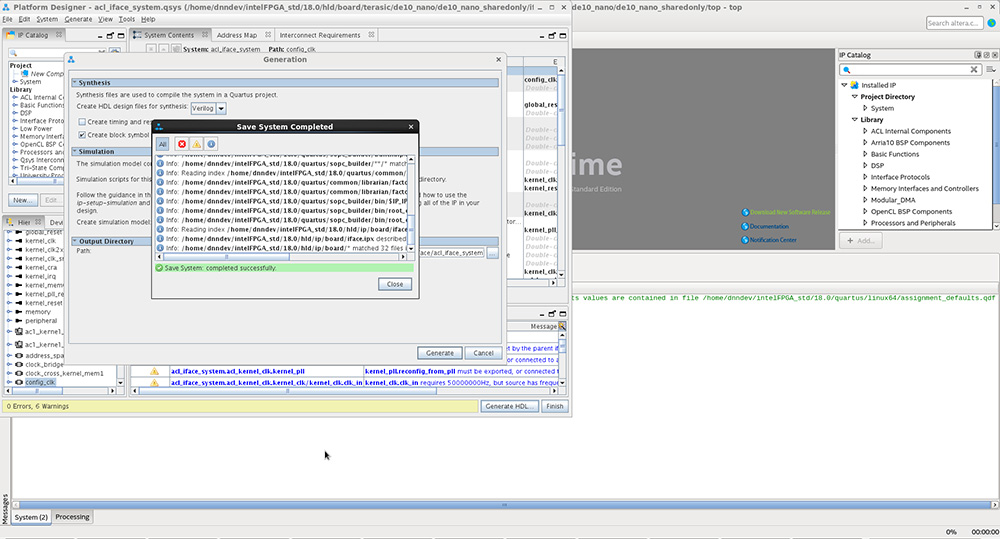

Sasve System Completed画面にSave System: completed successfullyの表示が出力されたら、Sasve System Completed画面のCloseボタンを選択します。

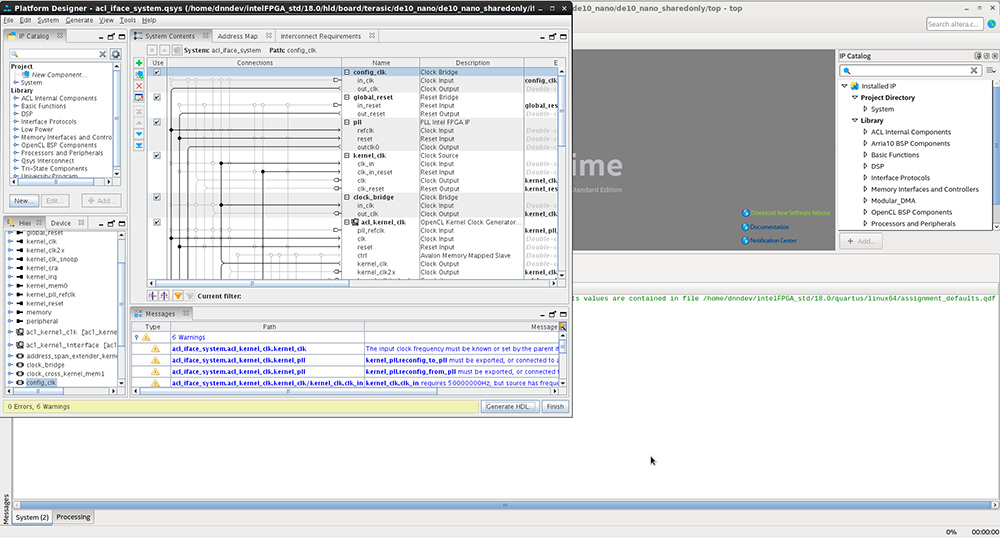

Platform Designer画面のFinishボタンを選択します。

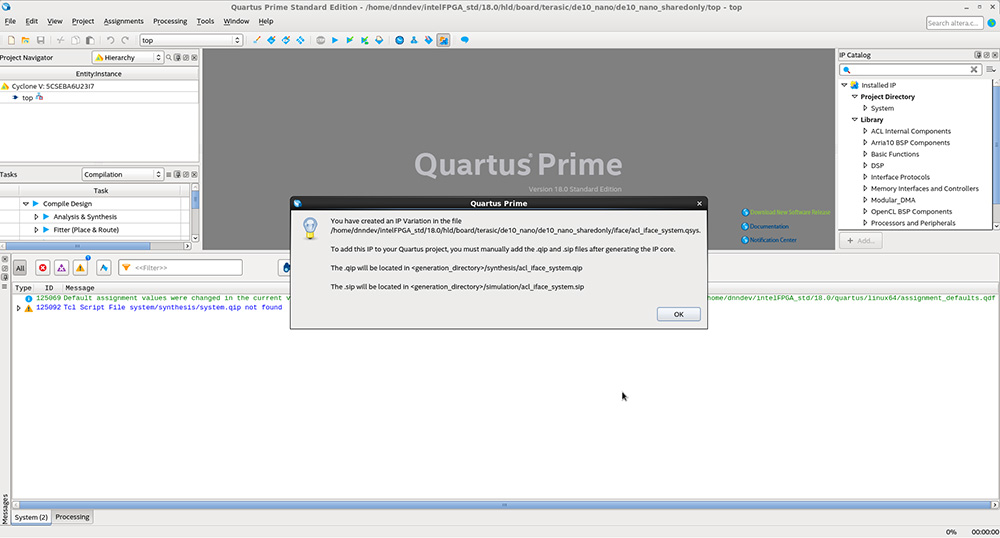

OKボタンを選択します。

Tools->Platform Designerを選択し、PlatfromDesignerのFile->Open..

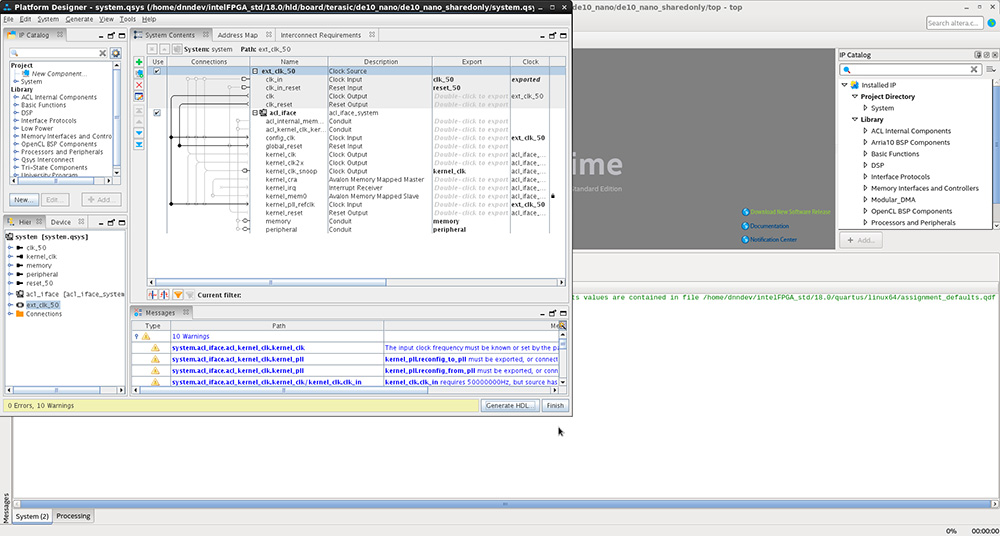

/home/dnndev/intelFPGA_std/18.0/hld/terasic/de10_nano/de10_nano_sharedonly/system.qsysを選択し、Openボタンを選択します。

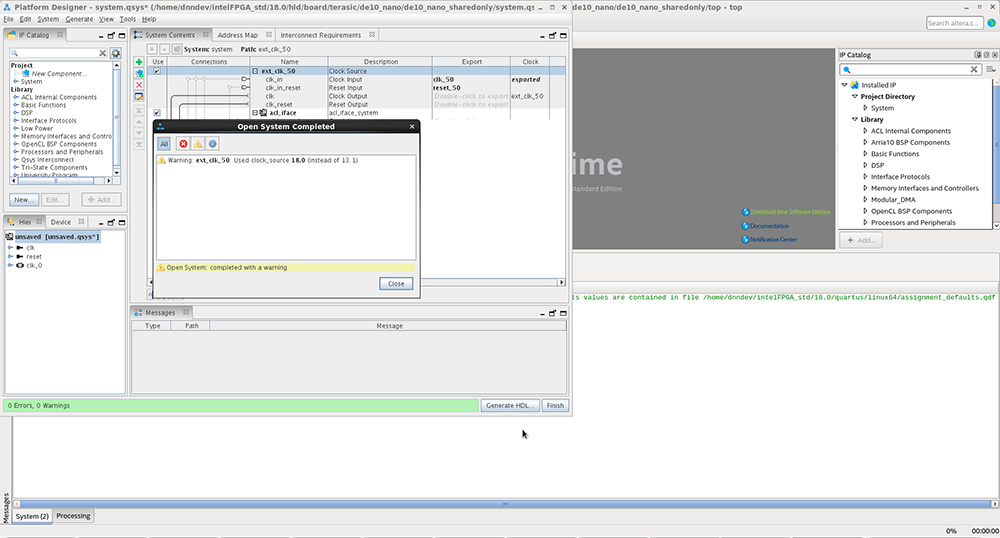

Open System Completed画面のCloseボタンを選択します。

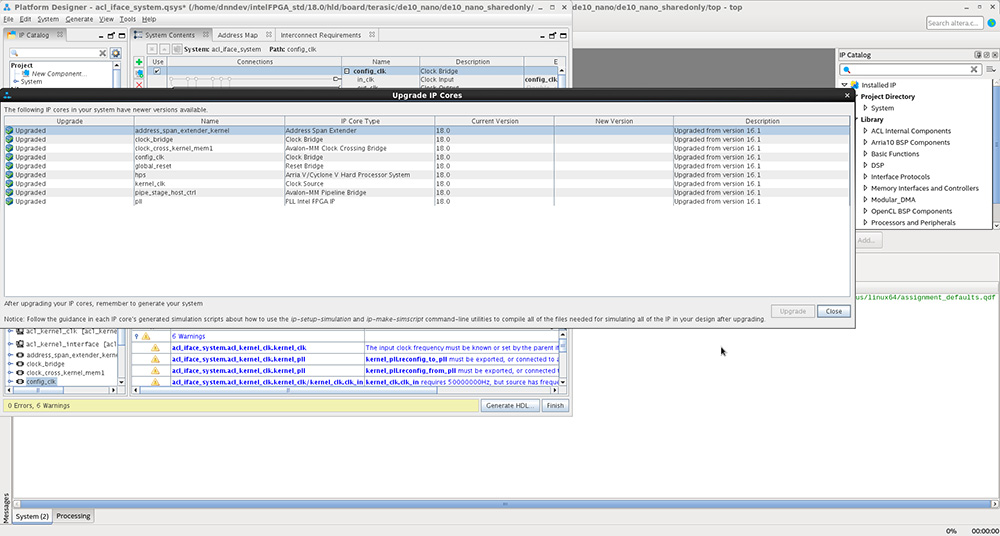

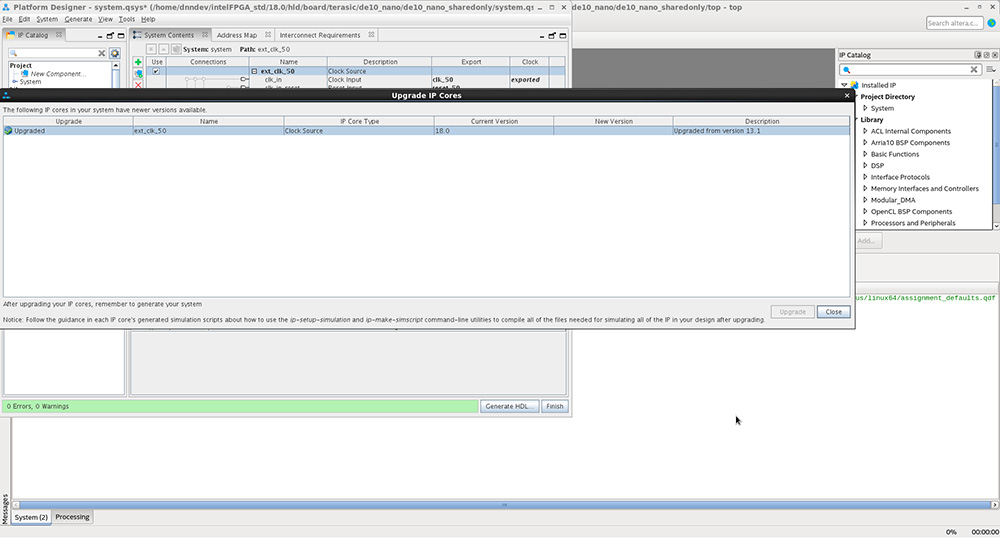

Upgrade IP Cores画面のCloseボタンを選択します。

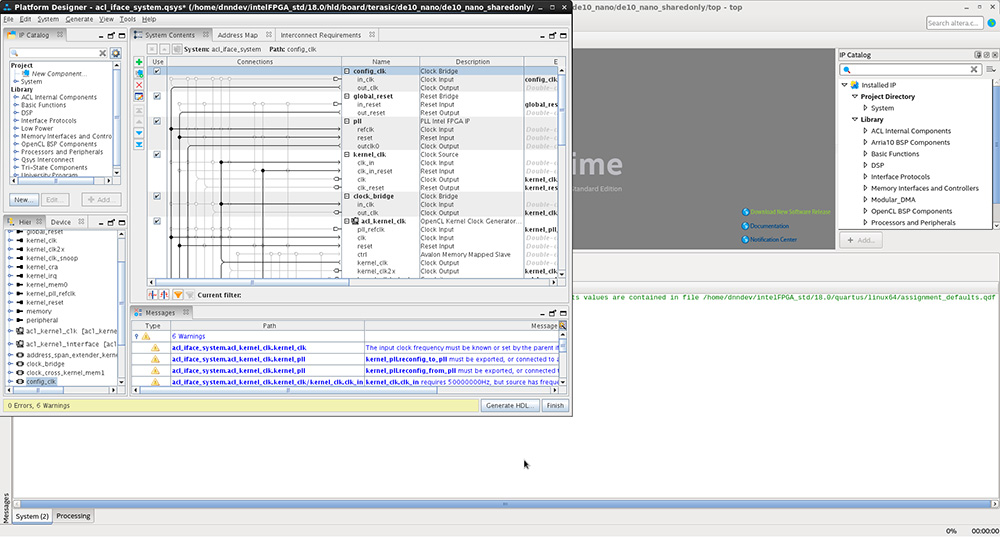

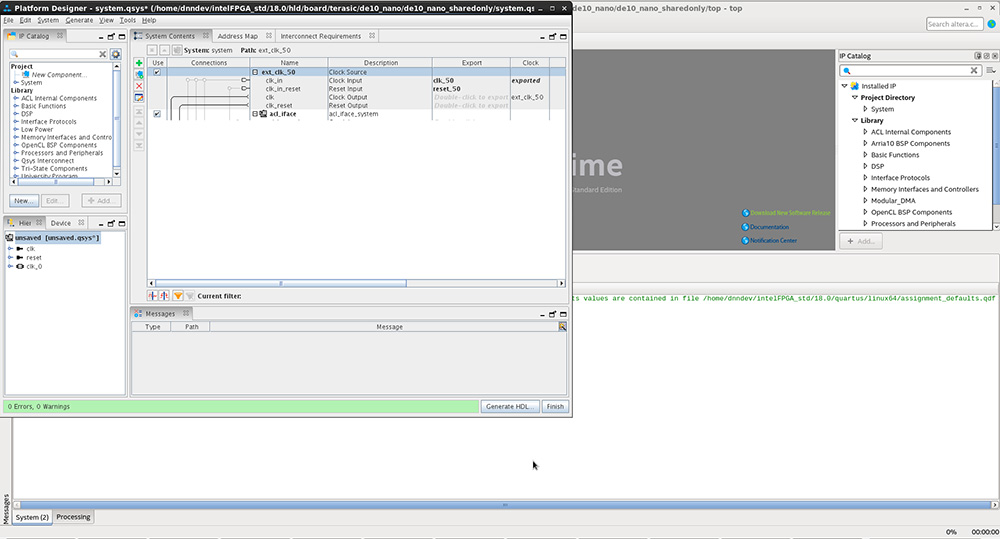

Generate HDL..ボタンを選択します。

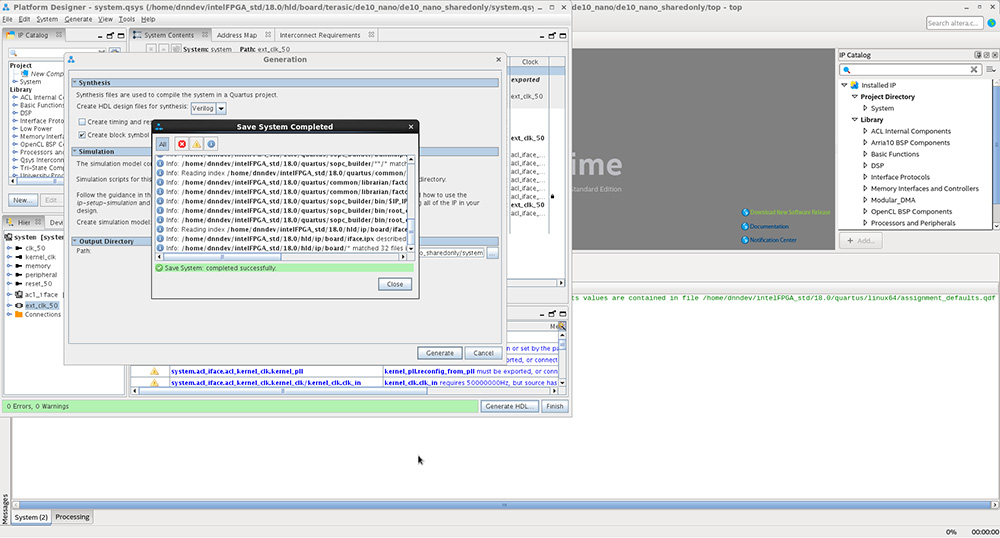

Generation画面のGenerateボタンを選択します。

Save System Completed画面にSave Ssystem: completed successfully.の表示が出力されたら、Save System Completed画面のCloseボタンを選択します。

Platform Designer画面のFinishボタンを選択します。

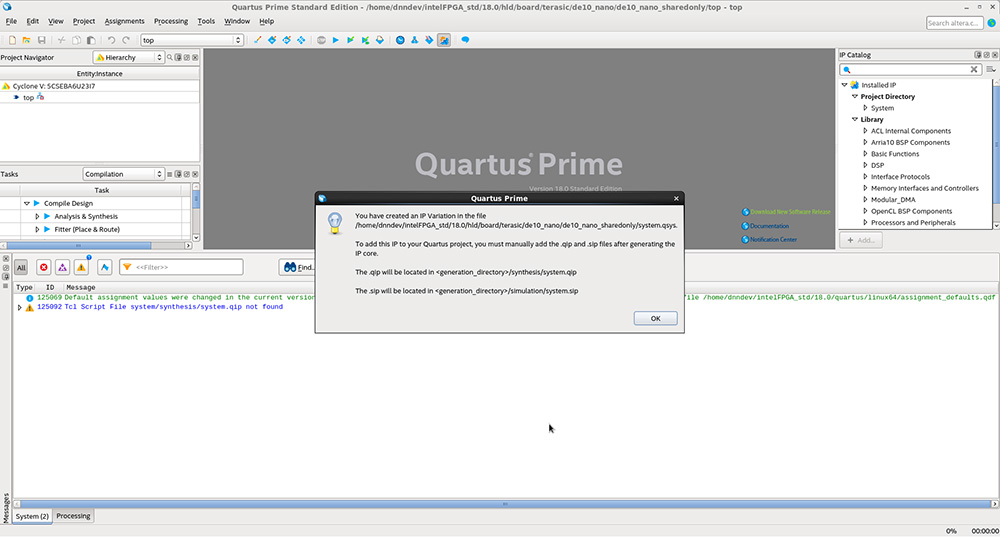

OKボタンを選択します。

File->Exitを選択します。

board_env.xmlを修正します。

16.1を18.0に修正します。

# cd /home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano

# vi board_env.xml

~~

~~

<board_env version=”18.0” name=”de10_nano”>

~~

~~

:wq

board_spec.xmlを修正します。

14.1を18.0に修正します。

# cd /home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/de10_nano_shardonly

# vi board_spec.xml

~~

~~

<board_env version=”18.0” name=”de10_nano_sharedonly”>

~~

~~

:wq

以上でDE10-nanoのOpenCL™BSPをインテル® FPGA SDK for OpenCL™ 18.0のプロジェクトが出来ました。

OpenCL™RTE(ランタイム環境)スタンダードエディション 18.0をインストールする。

OpenCL™RTEを利用するには、OpenCLドライバが含まれています。Linuxドライバをビルドするためには、Linuxカーネルが必要となります。

TERASIC社のDE10-nanoのOpenCL™BSPには、SDカードイメージが含まれていますが、Linuxカーネルが含まれていません。

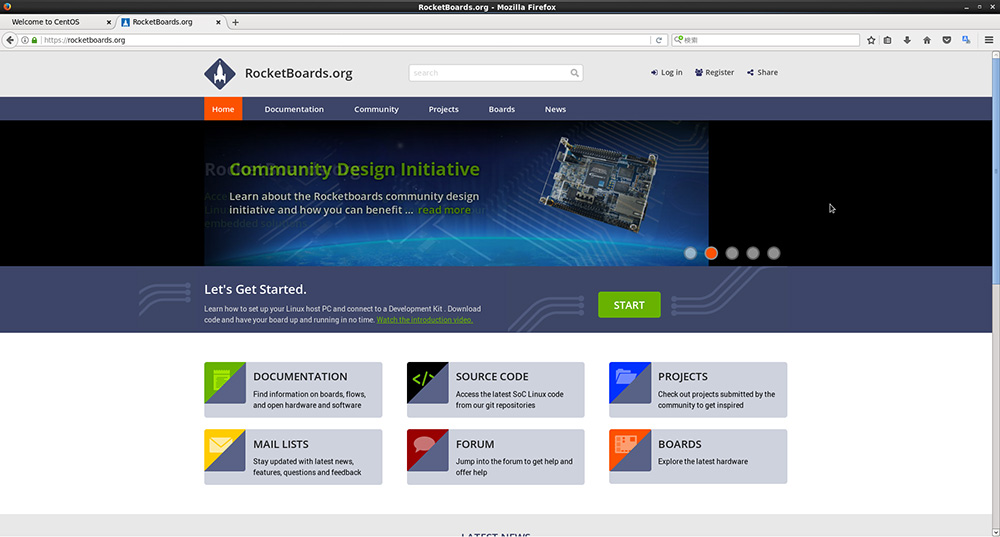

インテル® SoCFPGAのコミュニティサイトにRocketBoards.orgというサイトがあり、そこからLinuxカーネルのダウンロードが可能となっています。

最近ポリシーが変わり以前RocketBoards.orgにアップされていた(TERASIC社のDE10-nanoのOpenCL™BSPのSDカードに含まれていた)Linuxカーネルのダウンロードができません。

参考:https://rocketboards.org/foswiki/Documentation/GitGuidelines

なので・・・

TERASIC社のDE10-nanoのOpenCL™BSPのSDカードのLinuxカーネルごと更新しましょう!

というわけで、RocketBoards.orgからカーネルのダウンロードを行います。

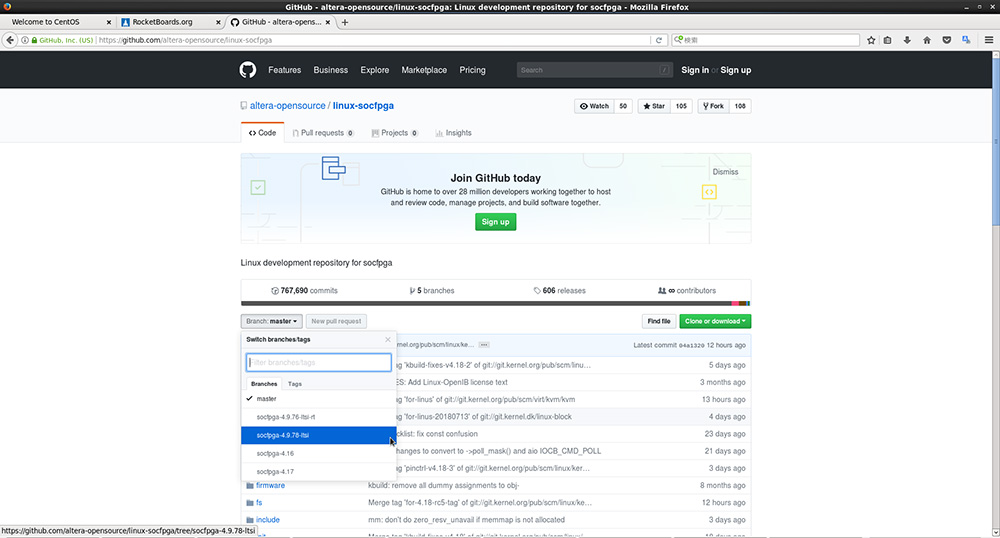

WebブラウザでRoectBoards.orgを表示します。

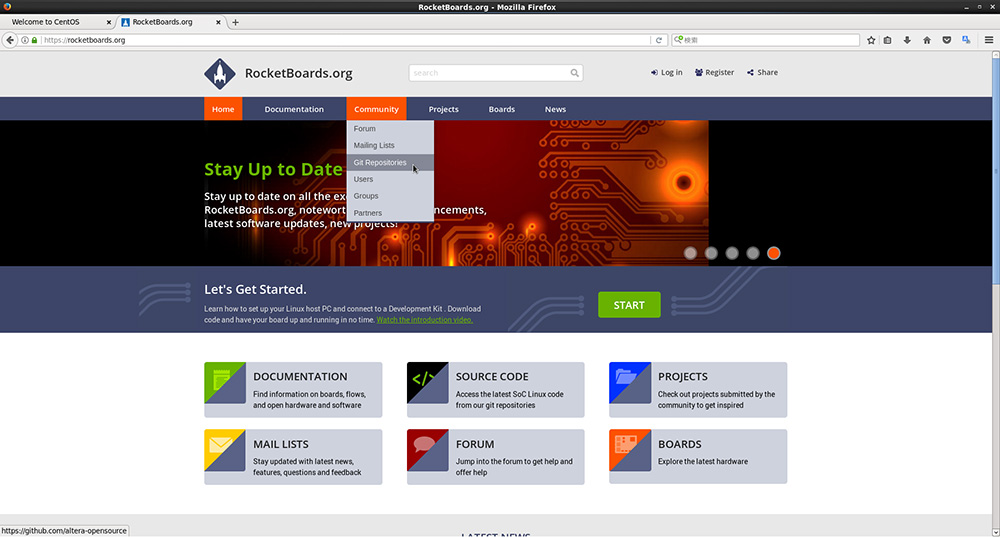

Community->Git Repositoriesを選択します。

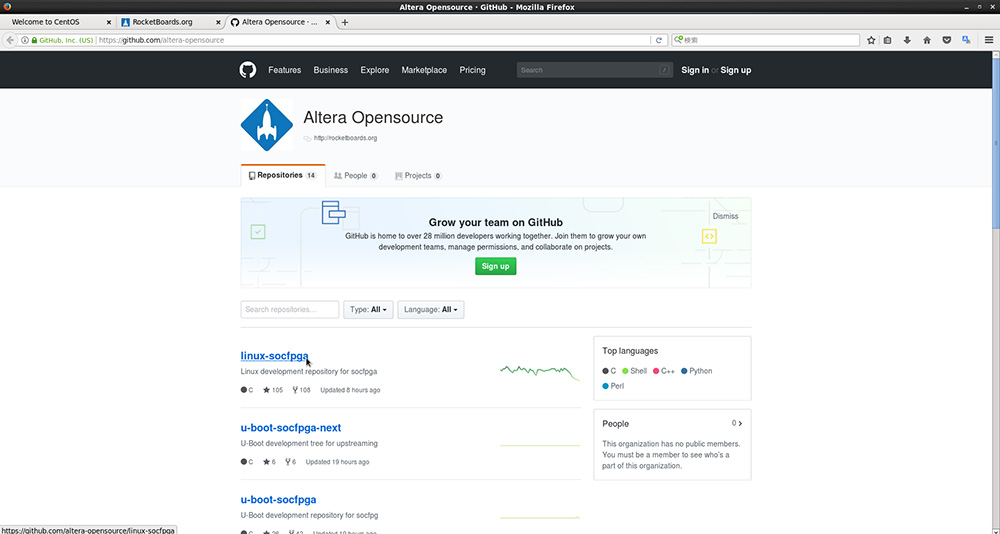

Linux-socfpgaを選択します。

Branch->socfpga-4.9-78-ltsiを選択します。

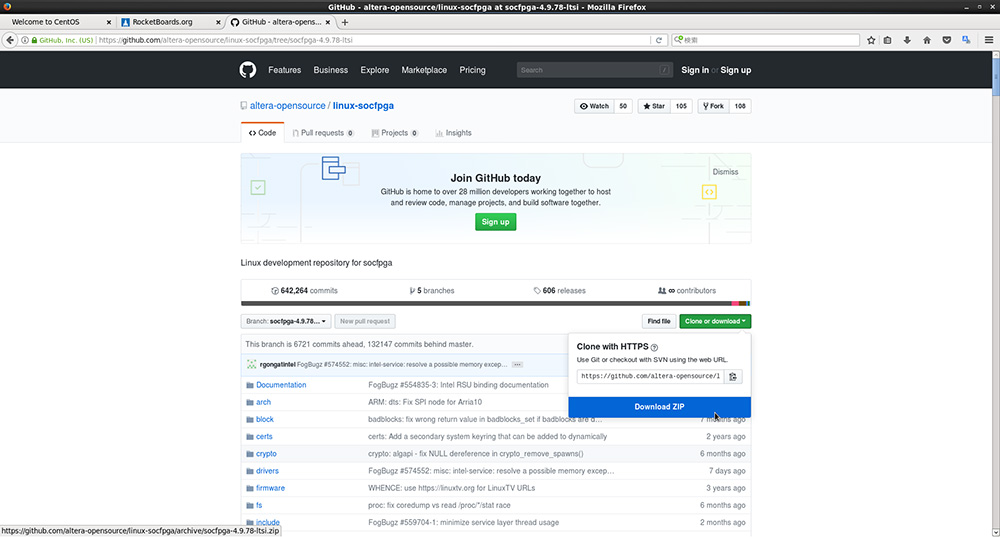

Clone or download->Download ZIPを選択するとカーネルのダウンロードが始まります。

Linuxカーネルのダウンロードが終わったら、Linuxカーネルのビルドを行いましょう!

下記のコマンドでLinuxカーネルのビルドを行います。

# cd ~

# source .quartus18.0.0.std.de10-nano

# cd /home/dnndev/intelFPGA_std/18.0/embedded/

# source ./embedded_command_shall.sh

~~

~~

# cd <linux_kernel_download_folder>

# unzip linux-socfpga-socfpga-4.9.78-ltsi.zip

~~

~~

# cd linux-socfpga-socfpga-4.9.78-ltsi

# export ARCH=arm

# export CROSS_COMPILE=arm-linux-gnueabihf-

# make socfpga_defconfig

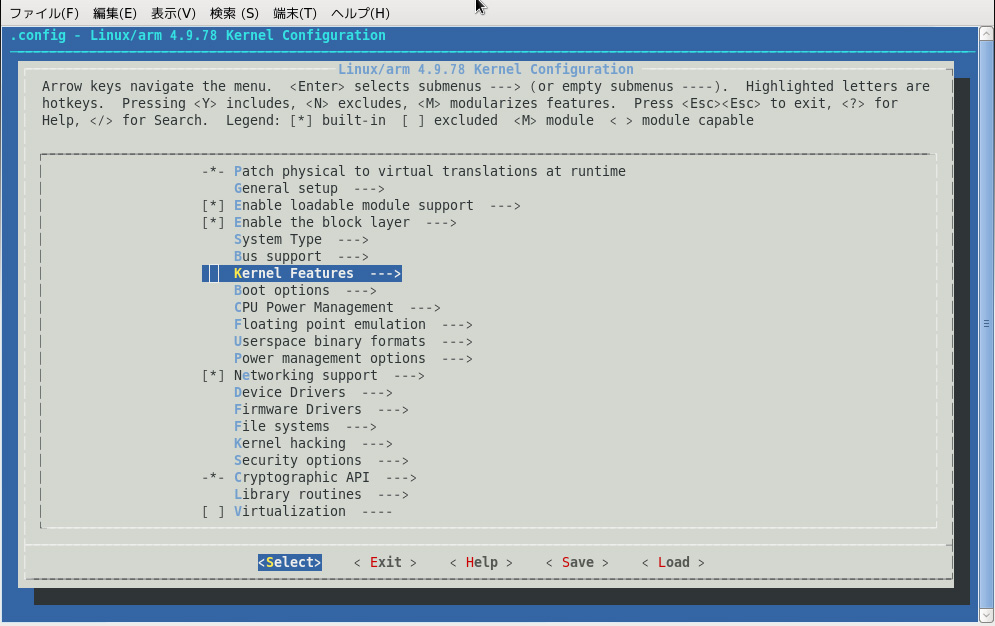

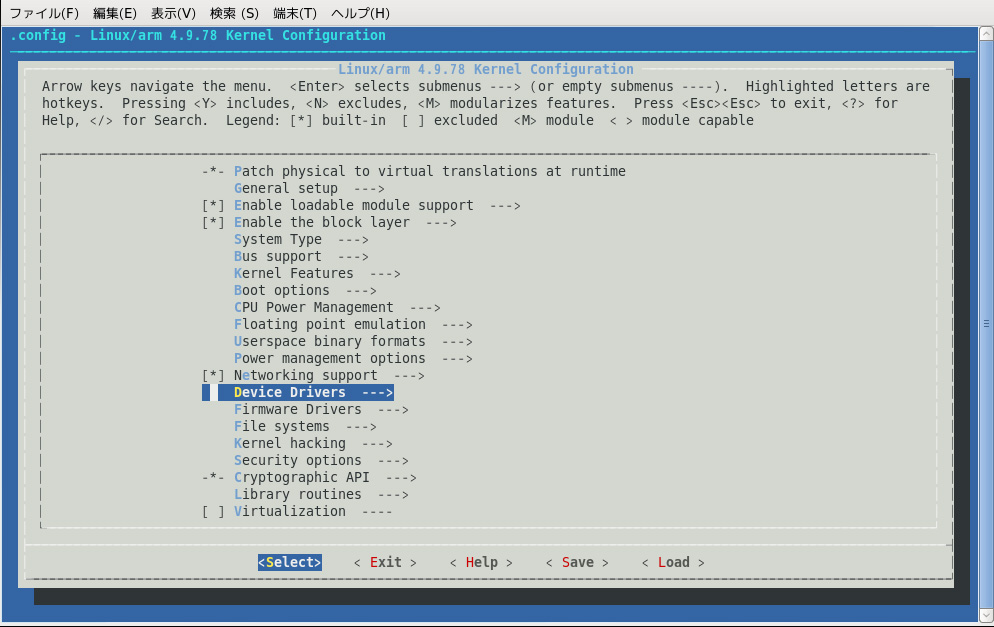

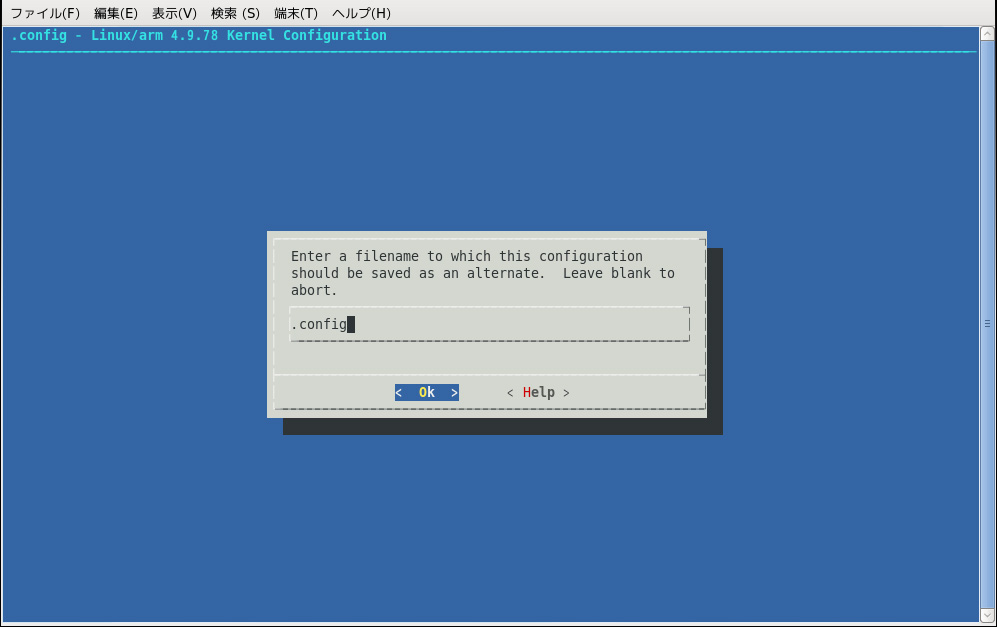

# make menuconfig

~~

~~

↑↓キーを利用してKernel Fuaturesを選択して←→キーを利用して<Select>を選択後、リターンキーを押します。

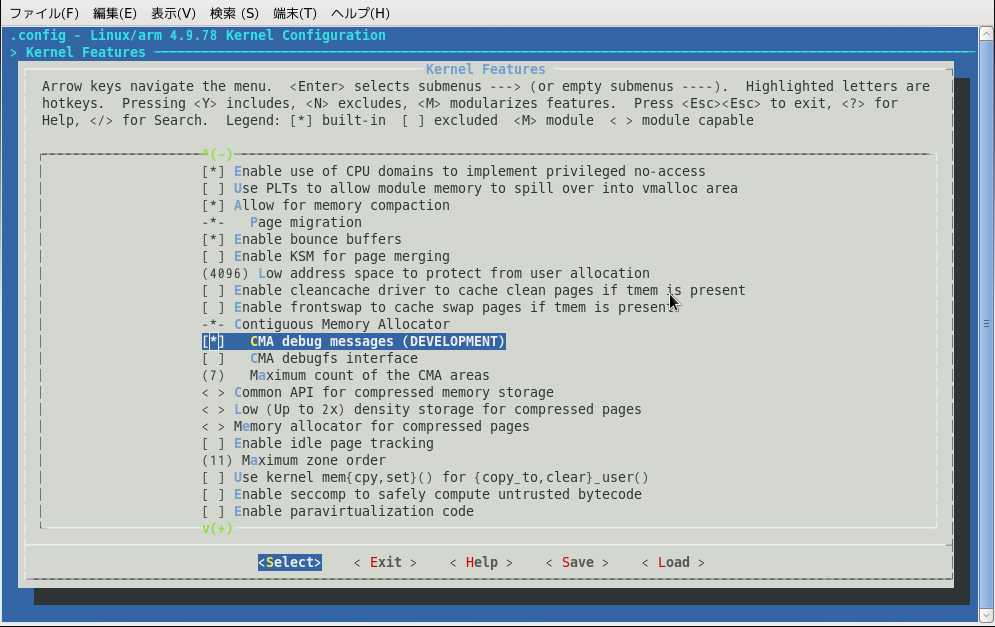

↑↓キーを利用してCMA debug messages (DEVELOPMENT)を選択して、

スペースキーを利用して[*]マークを付けます。

←→キーを利用して<Exit>を選択後、リターンキーを押します。

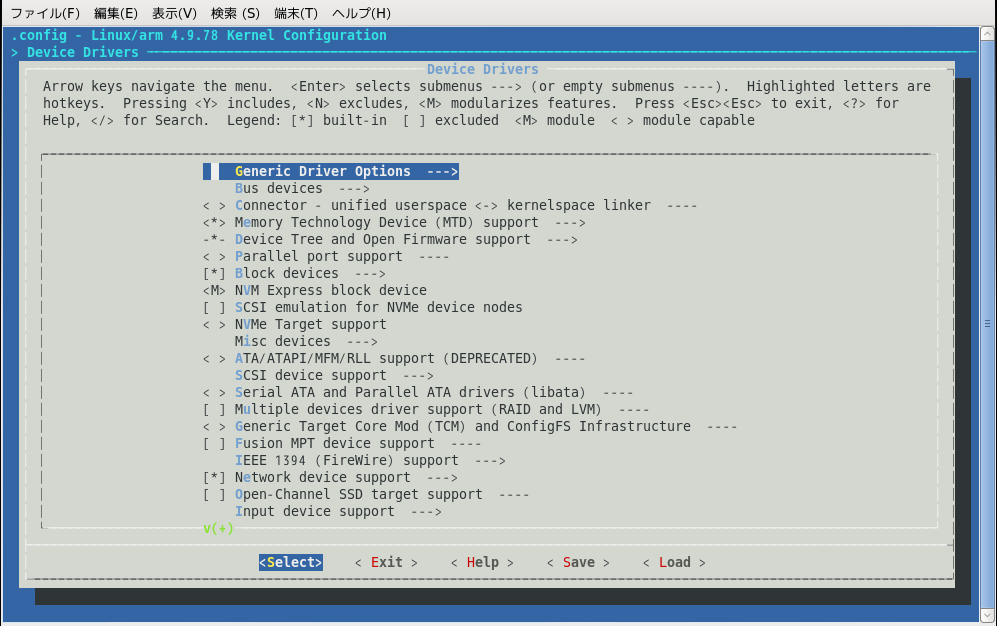

↑↓キーを利用してDevice Driversを選択して、←→キーを利用して<Select>を選択後、リターンキーを押します。

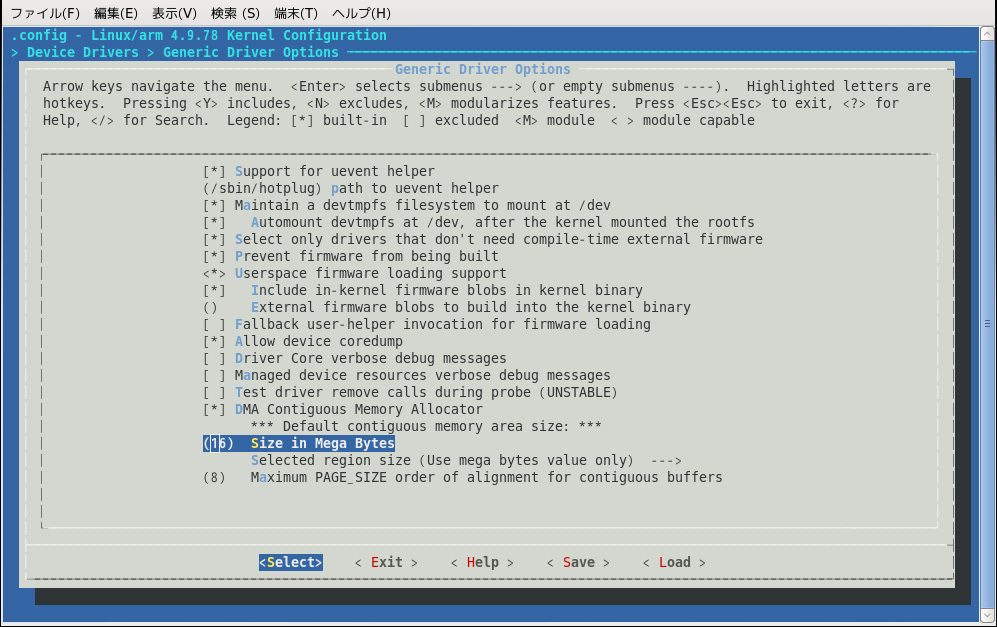

↑↓キーを利用してGeneric Driver Optionsを選択して、←→キーを利用して<Select>を選択後、リターンキーを押します。

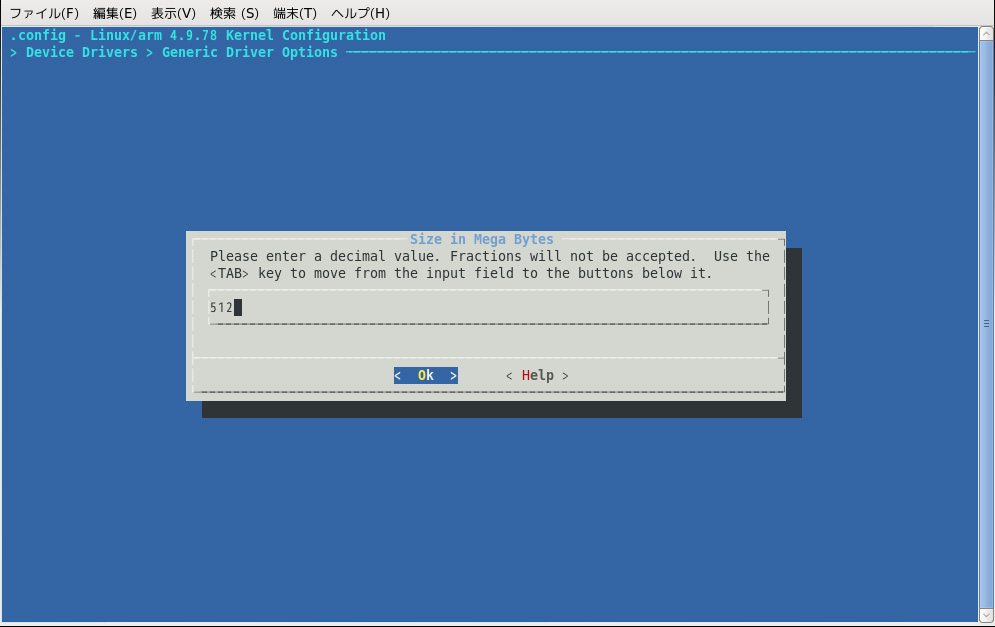

↑↓キーを利用してSize in Mega Bytesを選択して、←→キーを利用して<Select>を選択後、リターンキーを押します。

16の設定値を512に書き換えて<OK>を選択後、リターンキーを押します。

←→キーを利用して<Save>を選択後、リターンキーを押します。

←→キーを利用して<OK>を選択後、リターンキーを押します。

←→キーを利用して<EXIT>を選択後、リターンキーを押します。(これを何回か繰り返して終了します。)

下記コマンドによりカーネルのmakeを開始します。

# make

~~

~~

# make modules

~~

~~

# make zImage

~~

~~

# mkdir ../modules

# INSTALL_MOD_PATH=../modules make modules_install

Linuxカーネルのビルドが完了したので、

OpenCL™RTE(ランタイム環境)スタンダードエディション 18.0をビルドしましょう!

# cd ~

# source .quartus18.0.0.std.de10-nano

# cd /home/dnndev/intelFPGA_std/18.0/embedded/

# source ./embedded_command_shall.sh

~~

~~

# cd <opencl_rte_download_folder>

# mkdir aocl-rte-18.0.0-614.arm32

# cp aocl-rte-18.0.0-614.arm32.tgz aocl-rte-18.0.0-614.arm32

# tar xzvf aocl-rte-18.0.0-614.arm32/aocl-rte-18.0.0-614.arm32.tgz

# cd aocl-rte-18.0.0-614.arm32/board/c5soc/arm32/driver

# vi Makefile

~~

~~

#KDIR ?= /tools/aclboardpkg/.platform/linux-socfpga/linux-socfpga-socfpga-3.13-rel14.0/

KDIR ?=<ビルドしたlinuxカーネルソースコードへのパス>/linux-socfpga-socfpga-4.9.78-ltsi

~~

~~

:wq

# make clean

# make

以上で、OpenCL™RTE(ランタイム環境)スタンダードエディション 18.0をビルドが完了しました。

これで、インストールと環境構築がほぼ完了です!

次回はOpenCLサンプルデザインのビルドです。

※参考サイト:インテル® FPGAのサイト(https://www.altera.co.jp/products/design-software/embedded-software-developers/opencl/overview.html)

※各ツールのライセンスや購入に関しては、代理店・メーカにお問い合わせください。

※本コラムは、弊社が実際に開発をした中での経験より構成しております。本内容に準じて実施した結果については、本内容に準じて実施した結果に生じるいかなる影響、損害に関して、責任の無いものといたします。本コラムで紹介しておりますツールについては、合法性、正確性、道徳性、最新性、適切性、著作権の許諾や有無など、その内容については、何らの責任を負うものではありません。また、当社は通知することなく当サイトに掲載した情報の訂正、修正、追加、中断、削除等をいつでも行うことができるものとします。コンテンツのご利用により、万一、ご利用者様に何らかの不都合や損害が発生したとしても、当社は何らの責任を負うものではありません。

個別相談も承っております。下記よりお申し込みください。