COLUMN

ソフトエンジニア向けFPGAでOpenCL™を始めるっ!~OpenCLサンプルデザインのコンパイル~

今回は、「第3回 OpenCLサンプルデザインのコンパイル」です。

FPGAでOpenCL™を始めるのってソフトウェアエンジニアにとって技術的に敷居が高いと感じている方向けに、Intel®のFPGAを利用して数回にわたりコラムを掲載させて頂きます。

OpenCL™って何?という方は、こちらをどうぞ。FPGAの利点も記載されておりますのでご参照ください。

前回用意したファイルやフォルダは下記4種類ですね。

■TERASIC社のDE10-nanoのOpenCL™BSPの用意

フォルダロケーション:<home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano

■環境変数設定スクリプトの作成

フォルダロケーション:<home_folder>/

ファイル名:.quartus18.0.0.std.de10-nano

※前回の内容で間違いがありましたので、下記を修正してください。

誤:

AOCL_BOARD_PACKAGE_ROOT=”$QUARTUS_VERSION_DIR/hld/board/terasic/de10nano”

正:

AOCL_BOARD_PACKAGE_ROOT=”$QUARTUS_VERSION_DIR/hld/board/terasic/de10_nano”

■board_env.xmlの修正

フォルダロケーション:<home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano

ファイル名:board_env.xml

■board_spec.xmlの修正

フォルダロケーション:

<home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano/de10_nano_shardonly

ファイル名:board_spec.xml

※前回の内容で間違いがありましたので、下記を修正してください。

誤:

<board_env version=”18.0” name=”de10_nano_sharedonly”>

正:

<board_env version=”14.1” name=”de10_nano_sharedonly”>

■LinuxKernel/ドライバ・モジュールの準備

・コンパイル済みカーネル

フォルダロケーション:<kernel_sourcode_tree>/arch/arm/boot/

ファイル名:zImage

・ドライバ・モジュール

フォルダロケーション:<kernel_sourcode_tree>/../modules/lib/modules/4.9.78-ltsi/

■OpenCL(TM)ランタイムの準備

フォルダロケーション:<opencl_rte_download_folder>

boardtestとhello_worldのコンパイルをトライします。

関連ソリューション

(1)各種環境変数を設定します

# cd ~

# source ./

# ./SoCEDSSetup-18.0.0.614-linux.run

# cd <home_folder>/intelFPGA_std/18.0/ embedded/

# source ./embedded_command_shall.sh

~~

~~

#

(2)DE10-nanoのOpenCL™BSPフォルダに移動します。

# cd <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano

(3)DE10-nanoのOpenCL™BSPフォルダにexsamplesフォルダがあり、そのフォルダにいくつかサンプルがあります。まずはboardtestフォルダに移動します。

# cd exsamples/boardtest

OpenCL™にはホスト側のプログラムとFPGA上で実行されるOpenCL™Kernelがあります。

OpenCL™ホスト側のプログラムをコンパイルして、その後OpenCL™Kernel側のプログラムのコンパイルを行いましょう。

(4)OpenCL™ホスト側のプログラムをコンパイル

# make

~~

~~

host/reorder_ocl.cpp: In function ‘void ocl_transfer_to_device(unsigned int*, int, _cl_mem**)’:

host/reorder_ocl.cpp:163:36: error: ‘CL_MEM_BANK_2_ALTERA’ was not declared in this scope

int bank = (src[0] & 0x800000) ? CL_MEM_BANK_2_ALTERA : 0;

host/memspeed.cpp: In function ‘int memspeed(cl_platform_id, cl_device_id, cl_context, cl_command_queue, cl_program)’:

host/memspeed.cpp:181:26: error: ‘CL_MEM_BANK_1_ALTERA’ was not declared in this scope

case 0: memflags |= CL_MEM_BANK_1_ALTERA; break;

host/memspeed.cpp:182:26: error: ‘CL_MEM_BANK_2_ALTERA’ was not declared in this scope

case 1: memflags |= CL_MEM_BANK_2_ALTERA; break; ^

host/memspeed.cpp:183:26: error: ‘CL_MEM_BANK_3_ALTERA’ was not declared in this scope

case 2: memflags |= CL_MEM_BANK_3_ALTERA; break; ^

host/memspeed.cpp:184:26: error: ‘CL_MEM_BANK_4_ALTERA’ was not declared in this scope

case 3: memflags |= CL_MEM_BANK_4_ALTERA; break; ^

host/memspeed.cpp:185:26: error: ‘CL_MEM_BANK_5_ALTERA’ was not declared in this scope

case 4: memflags |= CL_MEM_BANK_5_ALTERA; break; ^

host/memspeed.cpp:186:26: error: ‘CL_MEM_BANK_6_ALTERA’ was not declared in this scope

case 5: memflags |= CL_MEM_BANK_6_ALTERA; break; ^

host/memspeed.cpp:187:26: error: ‘CL_MEM_BANK_7_ALTERA’ was not declared in this scope

case 6: memflags |= CL_MEM_BANK_7_ALTERA; break;

make: *** [Makefile:36: all] Error 1

恐らく、makeは失敗したかと思います。

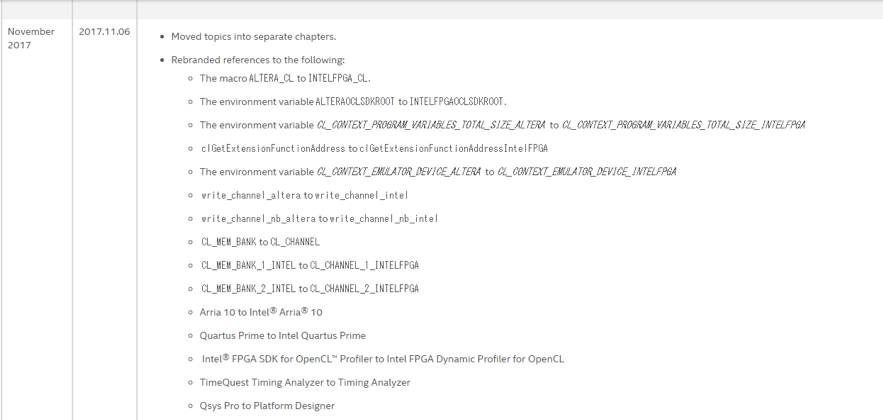

ALTERA社がIntel社によって買収されたタイミングでのバージョンアップで、各種定義が変更されています。

参考ドキュメント:インテル®FPGA SDK for OpenCL™プログラミング・ガイド

OpenCL™プログラミング・ガイドの最後の改版履歴にどのような定義変更があったか記載されています。

boardtestのコンパイルに関連する記述を下記に掲載します。

【bmp1.bmp】

CL_MEM_BANK_1_ALTERAをCL_CHANNEL_1_INTELFPGAに変更して、

同様にCL_MEM_BANK_2_ALTERAをCL_CHANNEL_2_INTELFPGAへ変更すると良さそうです。

reorder_ocl.cppとmemspeed.cppのエラーの行を全てこの様に修正しましょう。

再度コンパイルすれば、makeを実行したフォルダにboardtest_hostオブジェクトファイルが出来上がっています。

次は、OpenCL™Kernel側のプログラムのコンパイルを行いましょう。

(5)OpenCL™Kernel側のプログラムのコンパイル

# cd

# aoc -report -v -g boardtest.cl

aoc: Environment checks are completed successfully.

aoc: Cached files in /var/tmp/aocl/ may be used to reduce compilation time

You are now compiling the full flow!!

aoc: Selected default target board de10_nano_sharedonly

aoc: Running OpenCL parser….

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/examples/boardtest/device/boardtest.cl:53:14: error: Channel support is not enabled

channel uint kch;

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/examples/boardtest/device/boardtest.cl:58:3: error: function ‘write_channel_altera’ is not supported by the Intel(R) FPGA SDK for OpenCL(TM), and no user definition is provided

write_channel_altera(kch, arg);

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/examples/boardtest/device/boardtest.cl:58:3: error: function ‘write_channel_altera’ is not supported by the Intel(R) FPGA SDK for OpenCL(TM), and no user definition is provided

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/examples/boardtest/device/boardtest.cl:58:3: error: use of undeclared identifier ‘write_channel_altera’

/home/dnndev/intelFPGA_std/18.0/hld/board/terasic/de10_nano/examples/boardtest/device/boardtest.cl:64:9: error: function ‘read_channel_altera’ is not supported by the Intel(R) FPGA SDK for OpenCL(TM), and no user definition is provided

val = read_channel_altera(kch);

~~

~~

Error: OpenCL parser FAILED.

Refer to boardtest/boardtest.log for details.

#

今回もエラーが出たかと思います。

インテル® FPGA SDK for OpenCL™ のバージョンアップにより、baordtest.clを下記の通り修正して再度コンパイルしてください。

ソースコードの先頭の方に下記記述を追加・変更後、コンパイル

# vi boardtest.cl

~~

~~

#define REQD_WD_SIZE (1024*32)

# pragma OPENCL_EXTENSION cl_intel_channels : enable <=【追加】

~~

~~

# write_channel_altera(kch, arg) <=【コメントアウト】

write_channel_intel(kch, arg) <=【追加】

~~

~~

# read_channel_altera(kch) <=【コメントアウト】

read_channel_intel(kch) <=【追加】

~~

~~

:wq

# aoc -report -v -g boardtest.cl

~~

~~

aoc: First stage compilation completed successfully.

Compiling for FPGA. This process may take a long time, please be patient.

aoc: Hardware generation completed successfully.

#

コンパイルしたディレクトリにboardtest.aocxファイルが生成されています。

また、boardtestディレクトリのdevice/boardtestフォルダ内にtop.rbfが生成されている事を確認してください。

次は、hello_worldのコンパイルを行います。

(6)hello_worldのフォルダに移動します。

# cd <home_folder>/intelFPGA_std/18.0/hld/board/terasic/de10_nano

# cd exsamples/hello_world

(7)OpenCL™ホスト側のプログラムをコンパイル

# make

hello_worldディレクトリ内のbinフォルダ内にhello_worldオブジェクトファイルが出来上がっています。

(8)OpenCL™Kernel側のプログラムのコンパイル

# cd device

# aoc -report -v -g hello_world.cl

~~

~~

aoc: First stage compilation completed successfully.

Compiling for FPGA. This process may take a long time, please be patient.

aoc: Hardware generation completed successfully.

#

コンパイルしたディレクトリにhello_world.aocxファイルが生成されています。

以上で、boardtestとhello_worldのコンパイルが出来ました。

次回は、SDCardに書き込んで動かしてみましょう!

※OpenCL™のサンプルコードは下記にいくつかありますので、ご参考まで。

https://www.intel.com/content/www/us/en/programmable/products/design-software/embedded-software-developers/opencl/support.html

※参考サイト:インテル® FPGAのサイト

(https://www.altera.co.jp/products/design-software/embedded-software-developers/opencl/overview.html)

※各ツールのライセンスや購入に関しては、代理店・メーカにお問い合わせください。

※本コラムは、弊社が実際に開発をした中での経験より構成しております。本内容に準じて実施した結果に生じるいかなる影響、損害に関して、責任の無いものといたします。本コラムで紹介しておりますツールについては、合法性、正確性、道徳性、最新性、適切性、著作権の許諾や有無など、その内容については、何らの責任を負うものではありません。また、当社は通知することなく当サイトに掲載した情報の訂正、修正、追加、中断、削除等をいつでも行うことができるものとします。コンテンツのご利用により、万一、ご利用者様に何らかの不都合や損害が発生したとしても、当社は何らの責任を負うものではありません。

個別相談も承っております。下記よりお申し込みください。